FPGA并行浮点运算能力分析与比较

需积分: 0 70 浏览量

更新于2024-08-05

收藏 1.11MB PDF 举报

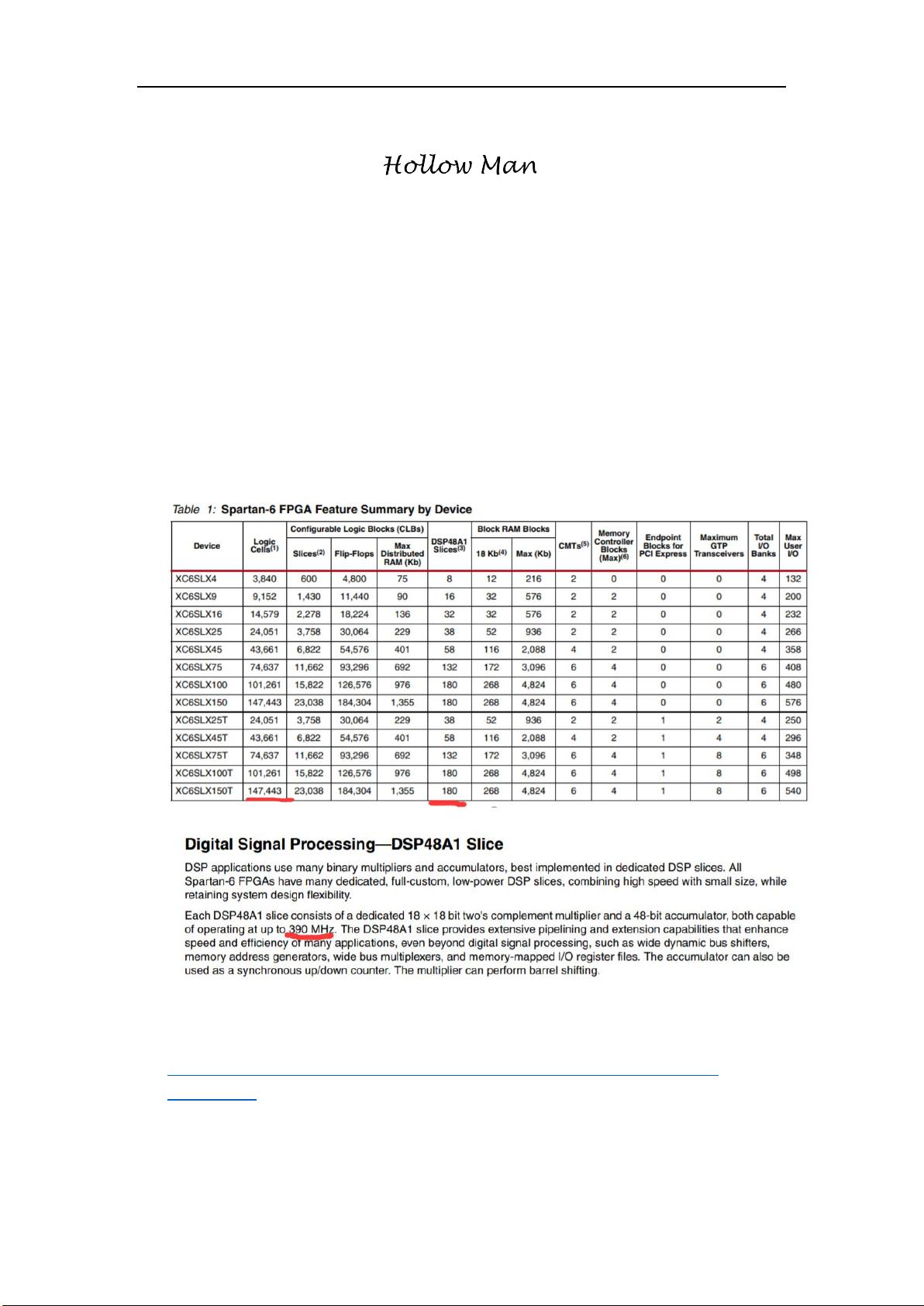

"本次作业是关于FPGA的并行单精度浮点数运算能力的评估,根据提供的链接中介绍的方法,结合Xilinx Spartan-6系列的FPGA为例,计算其FLOPS(浮点运算每秒次数)能力,并与Intel I7处理器进行对比。在Zynq UltraScale+ RFSoC ZU49DR这一高端FPGA上,进一步分析其硬件资源和运算潜力。"

在FPGA开发中,了解硬件资源的利用对于优化设计至关重要。FPGA的浮点运算能力可以通过计算其内部的DSP(数字信号处理)单元和逻辑单元(如LUT和DFF)的利用率来评估。公式FPGAFLOPS=DSP个数xDSP频率+逻辑单元个数x逻辑单元频率给出了计算方法。

以XC6SLX150T FPGA为例,它含有180个DSP48A1180单元和147443个LogicCells。由于1个基于DSP48的加法器需要2个DSP slices和289个LUT-FF pairs,而1个基于LogicCell的加法器需要517个LogicCells,考虑到I/O设备会占用一部分资源,约14000个。在最高390MHz的频率下,每个时钟周期可以执行2次单精度浮点运算。因此,XC6SLX150T的理论FLOPS计算结果为116.142GFLOPs。

相比之下,Intel的I7 6900K和6700K处理器的浮点数处理能力更强。这表明,在特定的运算密集型任务中,尽管FPGA可以提供高度并行的计算能力,但在单精度浮点运算的绝对性能上,高端的CPU仍然具有优势。

进一步考察Xilinx的Zynq UltraScale+ RFSoC ZU49DR,这款高端FPGA拥有930300个LogicCells和4272个DSP slices。同样假设I/O设备会占用约14000个LogicCells,剩余可用的LogicCells为916300个。由于Zynq UltraScale+平台的复杂性和高级功能,其能够支持更复杂的计算任务和更高的运算速度,理论上能够提供更高的FLOPS性能。

FPGA的优势在于其可编程性和并行性,可以针对特定应用进行定制化设计,以达到更高的效率。在设计时,需要考虑如何有效地分配和使用DSP slices、LUTs和DFFs,以及如何优化时钟频率,以最大化FPGA的计算性能。同时,与CPU相比,FPGA在能效比方面通常有更好的表现,特别是在大数据处理、机器学习和高速信号处理等领域。然而,理解和充分利用这些资源需要深入的硬件知识和编程技巧,这也是FPGA开发的一大挑战。

2022-08-03 上传

2022-08-08 上传

2023-06-06 上传

2023-05-29 上传

2023-10-07 上传

2024-09-24 上传

2023-10-21 上传

2023-10-31 上传

2023-06-10 上传

韩金虎

- 粉丝: 35

- 资源: 285

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍

已收录资源合集

已收录资源合集