FPGA设计思想与技巧:乒乓操作与流水线处理

需积分: 1 117 浏览量

更新于2024-09-14

收藏 203KB PDF 举报

"FPGA设计思想包括乒乓操作、串并转换、流水线操作和数据接口同步化,这些都是提高设计效率的关键技巧。"

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,允许设计者根据需要配置其内部逻辑块和互连资源,以实现特定的数字电路功能。在FPGA设计中,掌握一些核心的设计思想和技巧至关重要,能够显著提升设计的效率和性能。

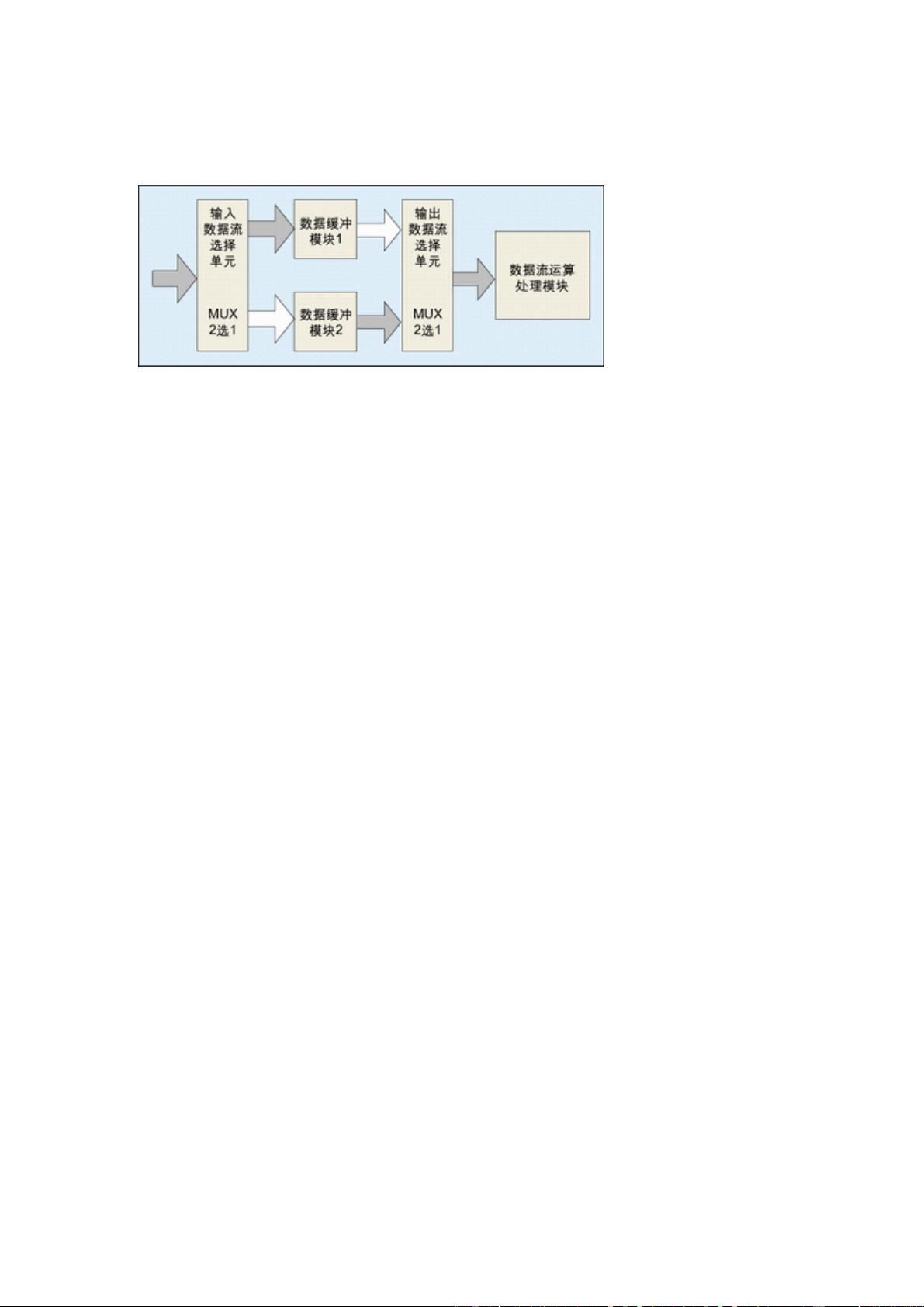

1. 乒乓操作:

乒乓操作是一种有效的数据流管理技术,常用于实时处理和流水线系统中。它利用两个或多个存储器(如双口RAM、单口RAM或FIFO)交替接收和提供数据,使得数据处理无需中断。例如,在一个缓冲周期内,数据被写入一个存储器,同时另一个存储器中的数据被读取并处理。这种操作方式确保了数据流的连续性,避免了处理延迟,尤其适用于需要连续无中断处理的数据流。

2. 串并转换:

串行到并行(Serdes)和并行到串行(Parades)转换是FPGA设计中的常见操作,主要用于提高数据传输速率和接口兼容性。串行化可以减少线路数量,降低布线复杂性,而并行化则可以在内部并行处理多个数据位,提升计算速度。这种转换通常结合移位寄存器和分布式RAM来实现。

3. 流水线操作:

流水线技术是FPGA设计中的重要优化手段,通过将处理任务分解为多个阶段,每个阶段在一个时钟周期内完成一部分工作,从而实现高吞吐量和低延迟。乒乓操作常与流水线设计相结合,确保数据在不同处理阶段间无缝流动。

4. 数据接口同步化:

在多时钟域的FPGA设计中,数据接口的同步是至关重要的,以防止时钟域间的 metastability(亚稳态)问题导致错误。通常使用同步器(如DFF或DLL)来确保在不同时钟域之间传递的数据是稳定和可靠的。

了解并熟练运用这些设计思想和技巧,可以帮助工程师更好地利用FPGA的并行处理能力,实现高效、低延迟和高带宽的设计。在实际应用中,如WCDMA基带处理,乒乓操作可以节省大量的缓冲区空间,而流水线和串并转换则能提高系统处理速率,适应高速数据流的处理需求。因此,对于FPGA初学者而言,深入理解和实践这些设计策略是非常有益的。

2018-12-03 上传

2012-12-30 上传

2010-01-16 上传

2020-07-02 上传

2021-02-07 上传

2018-12-03 上传

2019-05-25 上传

点击了解资源详情

点击了解资源详情

LCALS

- 粉丝: 0

- 资源: 1

最新资源

- AJAX开发简略.pdf

- PowerBuilder8.0中文参考手册.pdf

- struts2.0+hibernate3.1+spring2.0的使用.doc

- VB中与串口通讯需要用到的控件介绍

- cpu卡基础知识与入门方法

- c++ TR1 文档

- 虚拟键盘的驱动程序 制作虚拟键盘的过程和

- MRPII-最经典的教材

- GRAILS中文开发PDF文档

- c++ 小游戏 程序

- 深入浅出Struts2.pdf

- 网络工程师英词典 网工英语词汇表.pdf

- Ubuntu实用学习教程

- Linux.C++.Programming.HOWTO

- QTP初级使用手册QTP8_Tutorial_oldsidney_cn

- 注册表概述精华及普遍误区