Vivado设计流程详解:从工程创建到4位加法器设计

需积分: 0 161 浏览量

更新于2024-08-04

收藏 1.38MB DOCX 举报

Vivado设计流程实验手册详细介绍了Xilinx Vivado这款专业FPGA设计工具的使用方法,针对初学者和经验丰富的工程师提供了全面的指导。本手册主要围绕ProjectMode进行讲解,这是一种常见的设计模式,便于组织和管理项目。

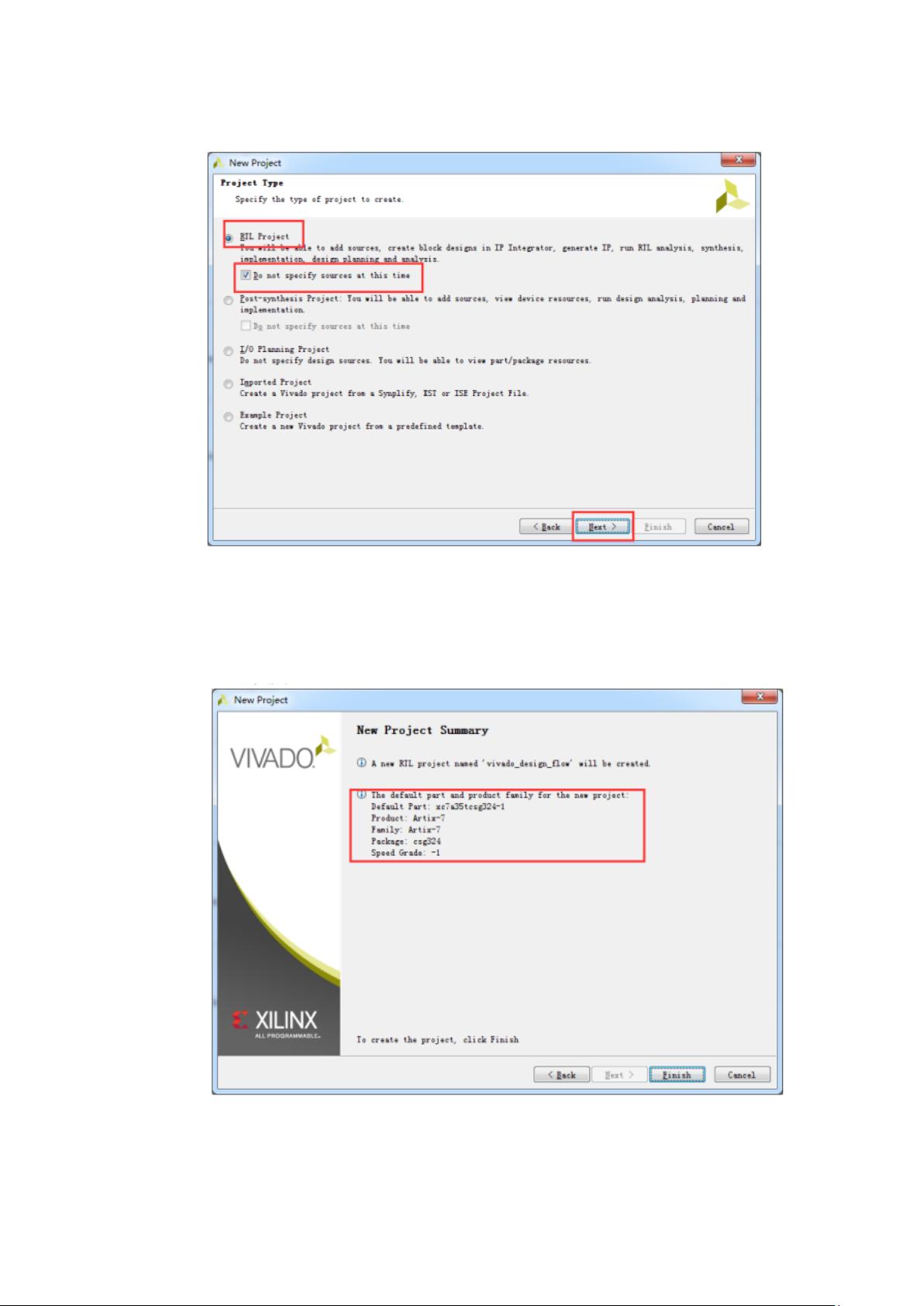

首先,新建工程是设计流程的关键步骤。用户需打开Vivado 2015.4开发工具,输入简洁且无特殊字符的工程名称,选择存储路径并在其中创建独立的子目录。选择RTL Project类型,暂时不指定源文件,以便后续添加。接着,根据实际使用的FPGA平台选择目标器件,确保配置的准确性。

设计文件的输入是整个流程的核心。用户通过Project Manager或者Sources对话框,选择AddorCreateDesignSources功能来添加或创建Verilog或VHDL源代码文件。如果需要新建文件,应选择CreateFile选项。在这个阶段,可以编写4位加法器等基础设计的源代码,为后续的逻辑编译做好准备。

行为仿真作为验证设计的重要环节,手册没有详述具体的步骤,但通常涉及编写testbench文件,通过时序分析和逻辑仿真检查设计的正确性和功能完整性。这一步骤可能包括设置输入波形、设置仿真时钟、观察和分析仿真结果等。

接下来是综合阶段,即将设计的硬件描述语言(HDL)转化为可编程逻辑器件的网表文件。在Vivado中,用户会看到设计视图和实施报告,确认设计是否符合预期。如有问题,可能需要调整电路结构或优化算法。

最后,是实现阶段,通过place-and-route工具对设计进行物理布局和布线,生成最终的硬件映射文件。这个过程会考虑到器件的资源限制和性能优化。完成所有步骤后,用户可以下载设计文件到目标FPGA进行烧录和测试。

这份实验手册涵盖了Vivado设计流程的全流程,从工程初始化到硬件实现,每一步都包含了必要的步骤和注意事项,旨在帮助读者掌握如何使用Vivado进行高效、精确的FPGA设计。无论是初次接触的入门者还是需要提升技能的专业人士,都可以从中获益匪浅。

2021-09-30 上传

2023-04-23 上传

2022-08-08 上传

2023-06-22 上传

2023-06-26 上传

2023-06-23 上传

2023-06-20 上传

2024-08-16 上传

2023-12-17 上传

高工-老罗

- 粉丝: 25

- 资源: 314

最新资源

- mattgirdler.github.io

- cloudinary_public:Dart包装器,可将媒体文件上传到cloudinary

- ulabel:基于浏览器的图像批注工具

- lickwolf.github.io

- .NET在线二手交易系统的ASP毕业设计(源代码+论文).zip

- mern-react:使用Javascript创建Staycation前端(ReactJS)

- Accuinsight-1.0.24-py2.py3-none-any.whl.zip

- js-algorithms:各种算法的 JavaScript 实现

- WebCursos

- workers-forms

- ajalabs_placeholder:AJAlabs.com当前的占位符网站

- 基于web的实验室管理系统毕业设计(自动排课功能的实现).zip

- fbfgbfqq

- 博客

- Qt6可进行录像录音代码特性

- voxel_survival

已收录资源合集

已收录资源合集