改进的增益增强共源共栅放大器:提升A/D转换器性能的关键

12 浏览量

更新于2024-08-30

收藏 455KB PDF 举报

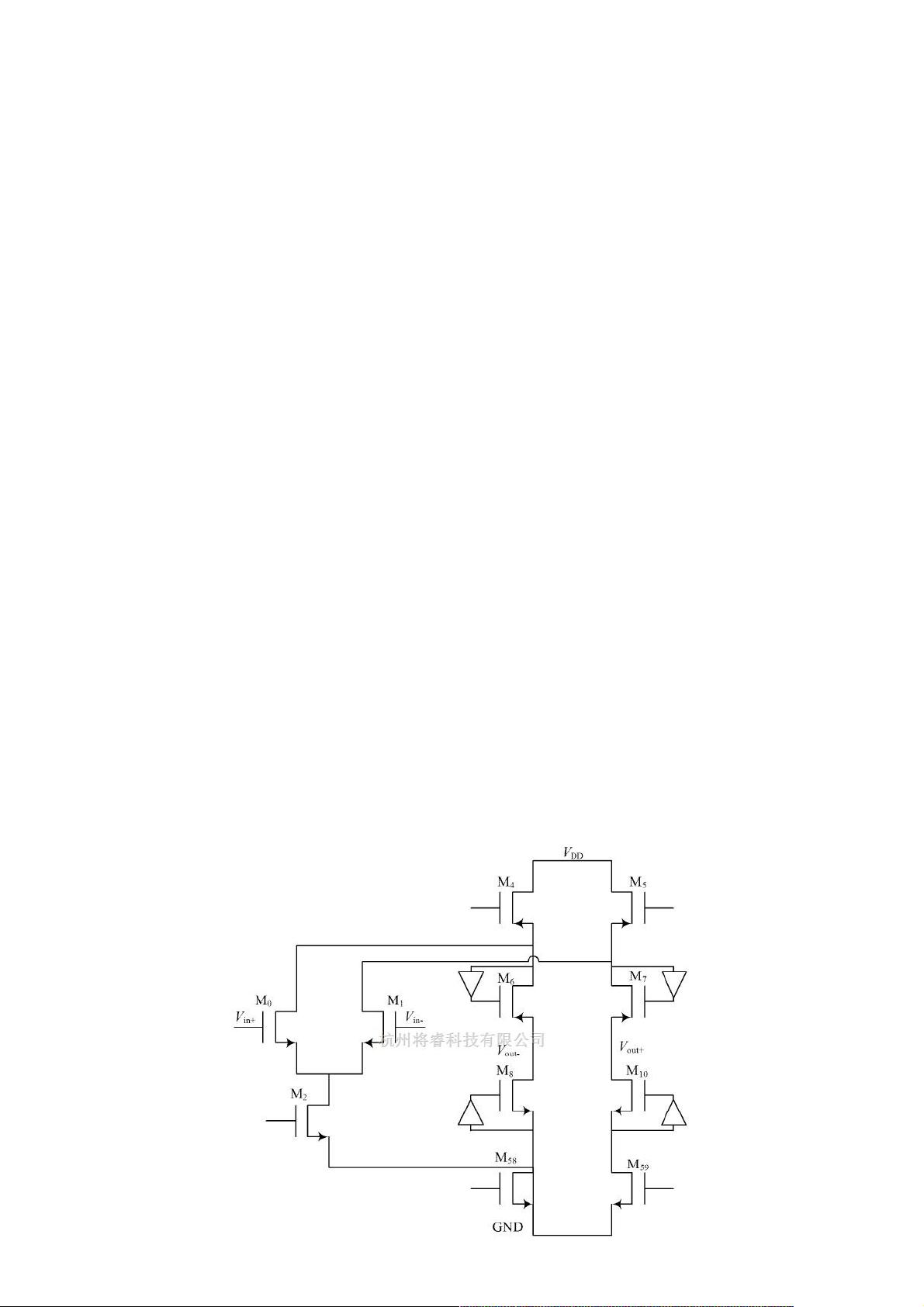

本文主要探讨了模拟技术中一种改进的增益增强共源共栅放大器的设计,这种放大器特别针对流水线A/D转换器的需求进行了优化。核心创新在于通过结合单端放大器的增益增强技术,实现了运算放大器在保持高直流增益的同时,显著地降低了面积占用和提高了版图匹配性。通过改良普通开关定容共模负反馈电路,设计者成功地减少了建立时间和放大器输出共模的抖动,从而提升了电路的稳定性。

电路的关键特性包括:采用SMIC 0.18微米CMOS工艺,仿真结果显示其小信号低频电压增益高达119.3分贝,单位增益带宽达到378.1兆赫兹,且相位裕度为60度。这些数值表明该放大器在高频性能上表现出色,对于模拟和混合信号集成电路设计来说至关重要,因为高性能运算放大器直接影响着整个电路系统的效能。

文章深入探讨了电路结构的分析与设计,特别提及了CMOS跨导运算放大器常见的两种结构——两级放大结构和套筒结构,以及折叠共源共栅结构。设计者选择了折叠共源共栅结构,利用开关电容共模反馈来进一步提升增益,同时保持折叠式设计的优势,如灵活性和小型化。

在设计过程中,为了兼顾性能和版图优化,选择单端放大器作为增益增强的辅助手段,这有助于控制电路复杂性和实现更好的集成。通过Cadence软件进行仿真验证,确保了设计的有效性和实际应用中的可靠性。

本文提供了一种创新的解决方案,不仅提升了运算放大器的性能指标,还满足了现代电路系统对于高精度、高速度和小型化的严苛需求,为模拟集成电路设计提供了新的可能。随着集成电路技术的持续进步,这种改进的增益增强共源共栅放大器将在未来的电路设计中发挥重要作用。

440 浏览量

527 浏览量

1019 浏览量

2021-03-19 上传

2025-01-04 上传

3795 浏览量

182 浏览量

6403 浏览量

2940 浏览量

weixin_38743481

- 粉丝: 698

- 资源: 4万+

最新资源

- skinrestorerfilegen

- katacoda方案:Katacoda方案

- 多功能便签效果

- JSPGenCMS 4.0 20160520

- SZFMBeadando

- XX种畜牧草良种繁殖场反季节蔬菜(萝卜)加工项目商业计划书.zip

- 开店损益评估表excel模板下载

- 电子邮件地址:Spring Cloud的餐厅服务,餐厅和餐厅

- capecodseedcoop

- html5lib-0.999999999.tar.gz

- Cloth-simulation:使用质量弹簧模型模拟布料

- vicky:Vicky 是使用 ffmpeg 将视频文件转换为声音文件的 GUI 程序

- perl-orm-easy:PostgreSQL数据库内ORM

- onlineSystem:基于SSH + BootStrap的在线考试系统

- 商场设计CAD图纸

- Dizi Haberleri-crx插件