Altera时序详解:快速入门与实践

需积分: 9 101 浏览量

更新于2024-07-18

收藏 15.39MB PDF 举报

本文档是关于Altera FPGA时序分析的基础教程,旨在帮助读者快速理解并掌握FPGA设计中的关键概念和实践技巧。主要内容涵盖以下几个部分:

1. **时序分析基础概念**:首先介绍了同步逻辑的时延模型,包括时钟抖动与偏斜、建立时间(Setup Time)、保持时间(Hold Time)、恢复时间(Recovery Time)和移除时间(Removal Time),以及LaunchEdge和LatchEdge的概念。此外,还讨论了数据和时钟之间的时序关系。

2. **时序分析基本公式**:详细解释了如何通过公式来检查不同类型的时序参数,如建立时间、保持时间和恢复时间的设定限制,以及多周期路径(Multicycle Paths)的考虑。

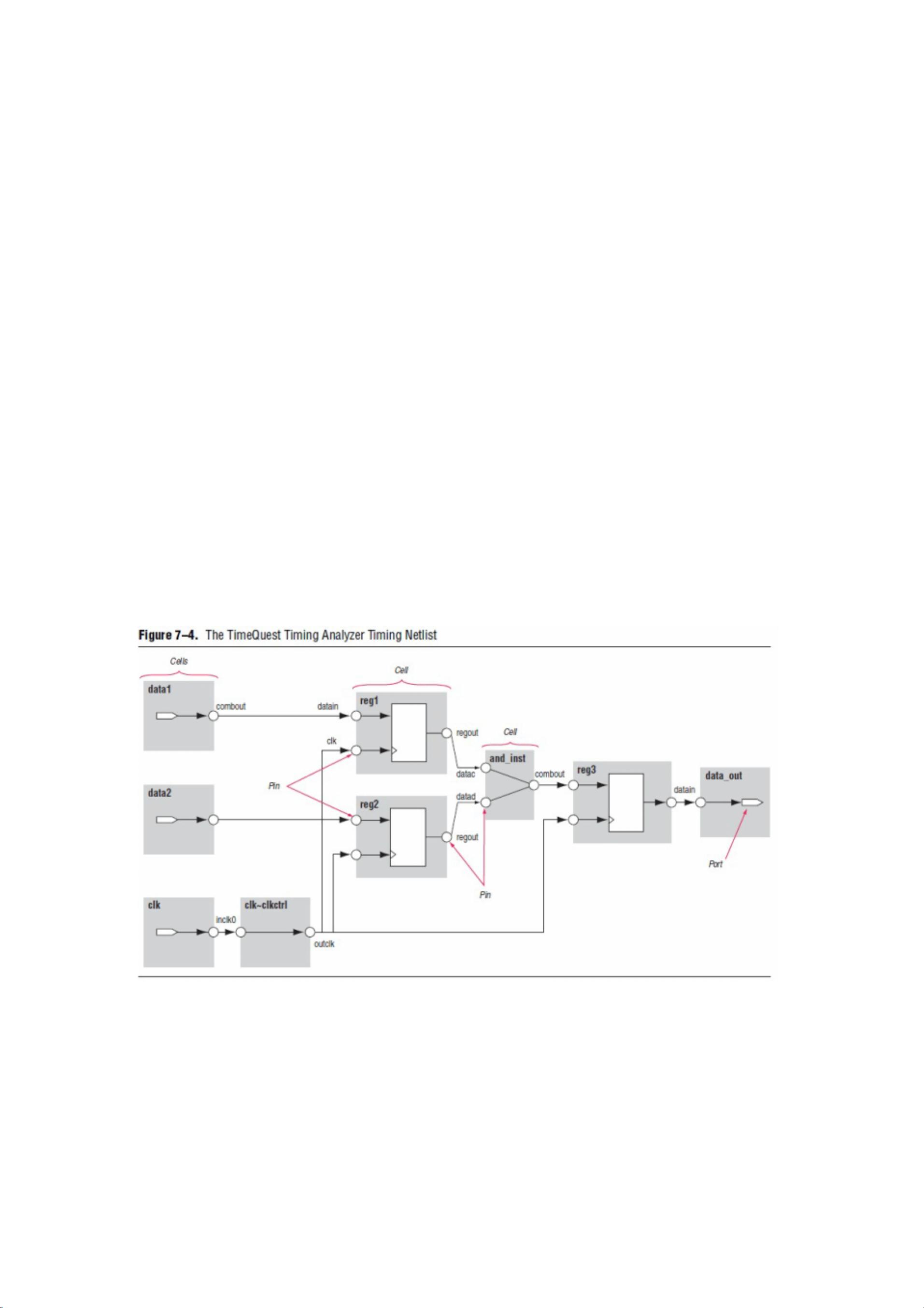

3. **Altera器件时序模型**:介绍了Altera FPGA特有的时序模型,包括基本单元和时序路径,以及如何理解和优化关键路径以提高设计性能。

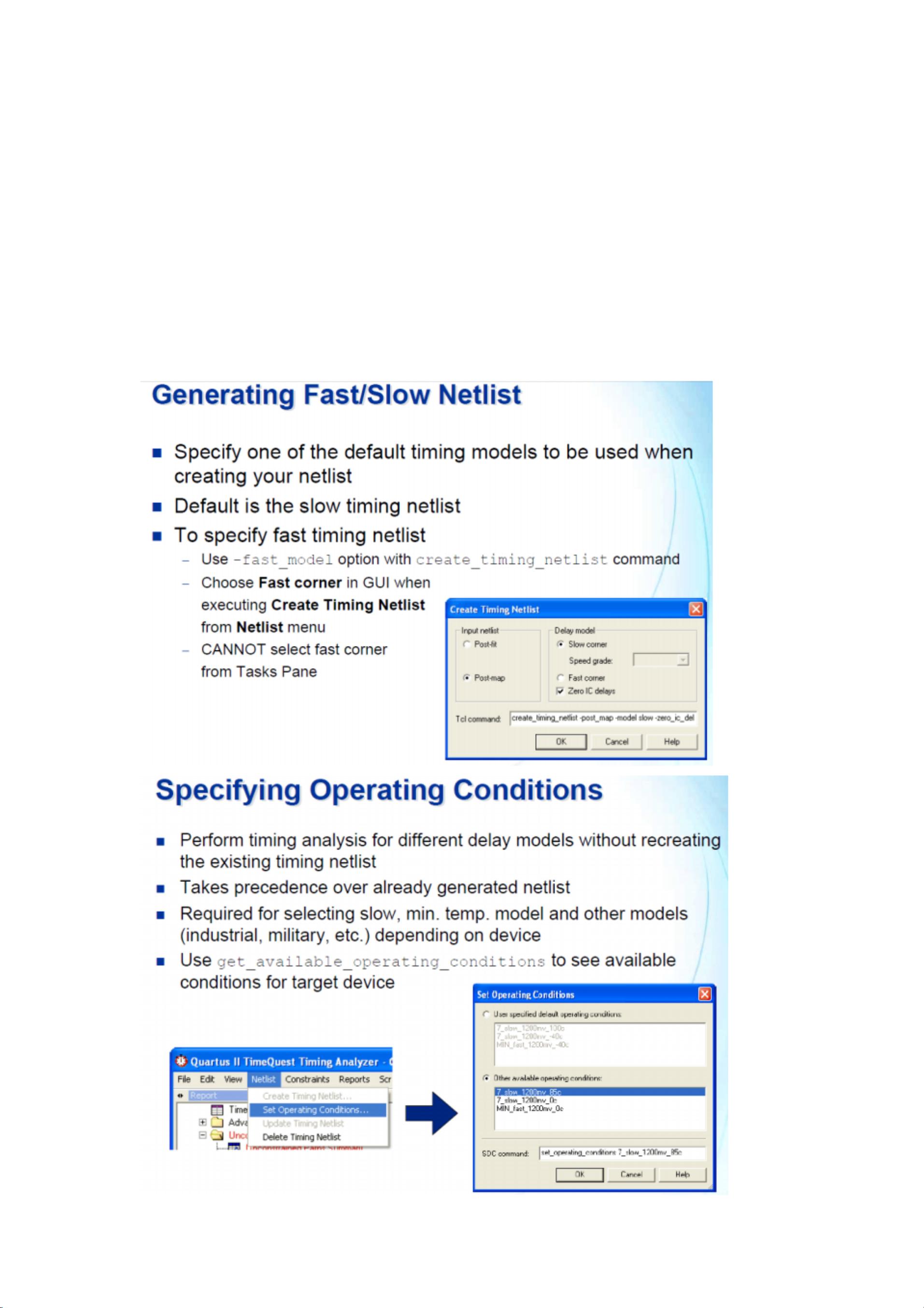

4. **时序约束的方法**:这部分着重于FPGA时序约束的几种策略,如使用Timequest时序分析工具。Timequest是一个强大的工具,它包括创建时钟、生成时钟、PLL时钟处理、自动时钟检测、默认约束设置、时钟延迟分析、不确定性处理以及去除常见时序悲观估计等步骤。

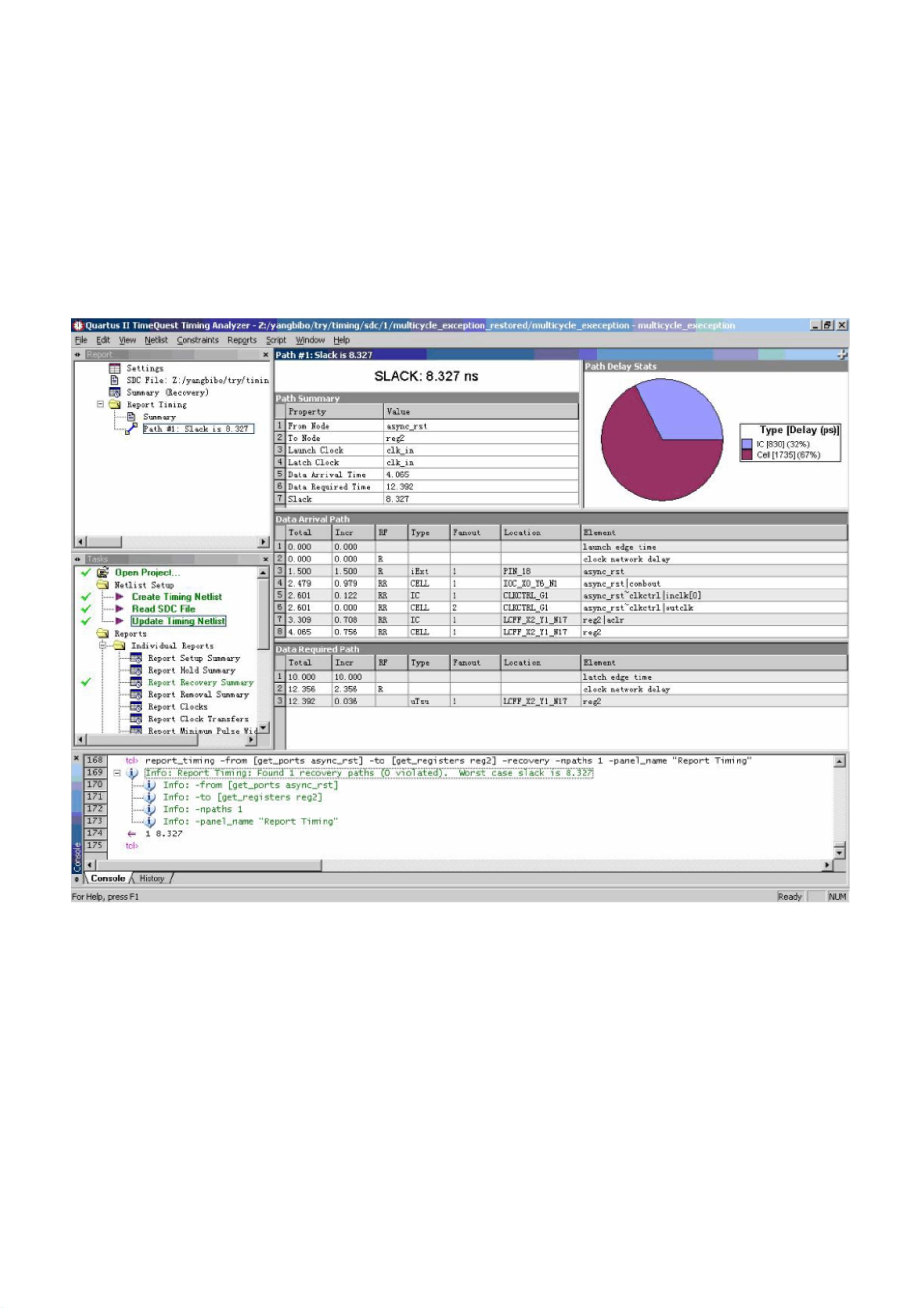

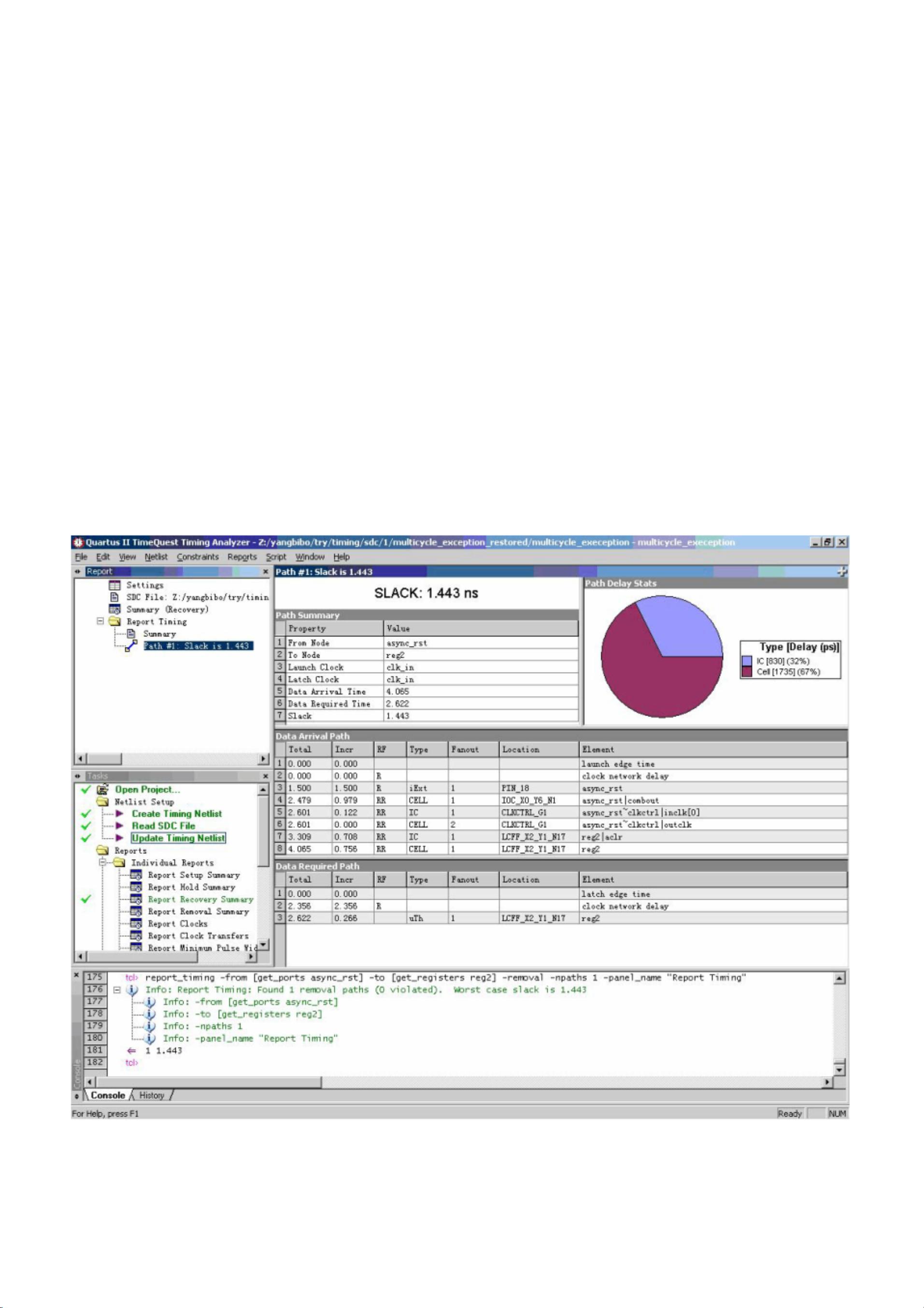

5. **Timequest应用**:深入讲解了如何在Timequest中进行时序分析,包括约束流程、图形用户界面的理解,以及如何解读时序波形图和计算时序余量,特别是针对Setup Time和Multicycle Paths的实例。

6. **具体的时序约束设置**:详细说明了针对输入输出(I/O)的不同接口类型(组合逻辑I/O和同步逻辑I/O)进行时序约束的方法,包括创建I/O引脚、设置合适的时钟配置等。

通过阅读这篇教程,学习者将能够理解FPGA设计中的时序至关重要,并掌握如何有效地使用Timequest进行时序分析和优化,从而确保设计满足Altera器件的时序要求,避免潜在的设计问题。对于想要进入FPGA领域或提升现有技能的工程师来说,这是一份非常实用的参考资料。

141 浏览量

180 浏览量

点击了解资源详情

157 浏览量

2025-01-06 上传

315 浏览量

170 浏览量

有边界才自由

- 粉丝: 2

最新资源

- 安卓动画库Persei:Yalantis开源动画的Java实现

- 掌握整流电路原理及应用的免费学习教程

- 意法半导体STM32F2xx固件库使用详解

- IC卡数据读写工具 - M1卡扇区信息获取

- Luban压缩算法:图片优化的未来之星

- Maya动画练习:16个动物角色模型绑定指南

- C#代码挑战解决方案集锦

- Python工厂操作系统开发教程

- SSMA环境搭建指南:从安装到使用

- 蓝宙双电机编码器检测程序功能详解

- Opencart VQMOD扩展实现多文件上传功能

- 新Twitter界面的极简主义主题设计

- 掌握C语言实现经典密码算法教程

- Angular开发环境搭建与代码脚手架使用指南

- 如何将Excel文件转换为TXT格式

- 使用JavaScript实现coinflip翻硬币效果