理解静态时序分析:ALTERA时序分析模型详解

"这篇文档是ALTERA公司的培训材料,涵盖了静态时序分析的基本原理和时序分析模型。文档旨在帮助用户深入理解时序分析,并在Quartus® II软件设计中进行有效的时序验证。"

在数字集成电路设计中,时序分析是确保电路正确运行的关键步骤。它涉及到对设计中的每个路径进行分析,以满足特定的时序规范或要求。时序分析的主要目标是防止由于延迟问题导致的功能错误,这在高速和高性能的系统中尤其重要。

静态时序分析(Static Timing Analysis,STA)是一种不依赖于模拟过程的分析方法,它能快速、准确地检测出设计中的时序问题,相比门级仿真和板级测试,能更快地发现与时序相关的错误。这种方法在现代数字设计流程中扮演着核心角色,因为它能够在布局布线阶段预测电路的性能。

在Quartus® II软件中,设计师需要输入时序要求和异常,这些信息将指导适配器在放置和路由过程中优化设计。时序要求包括时钟路径的延迟限制,以及数据传输和控制信号的建立时间与保持时间等。时序分析会对比实际设计结果与预设的时序规格,以确定设计是否满足性能目标。

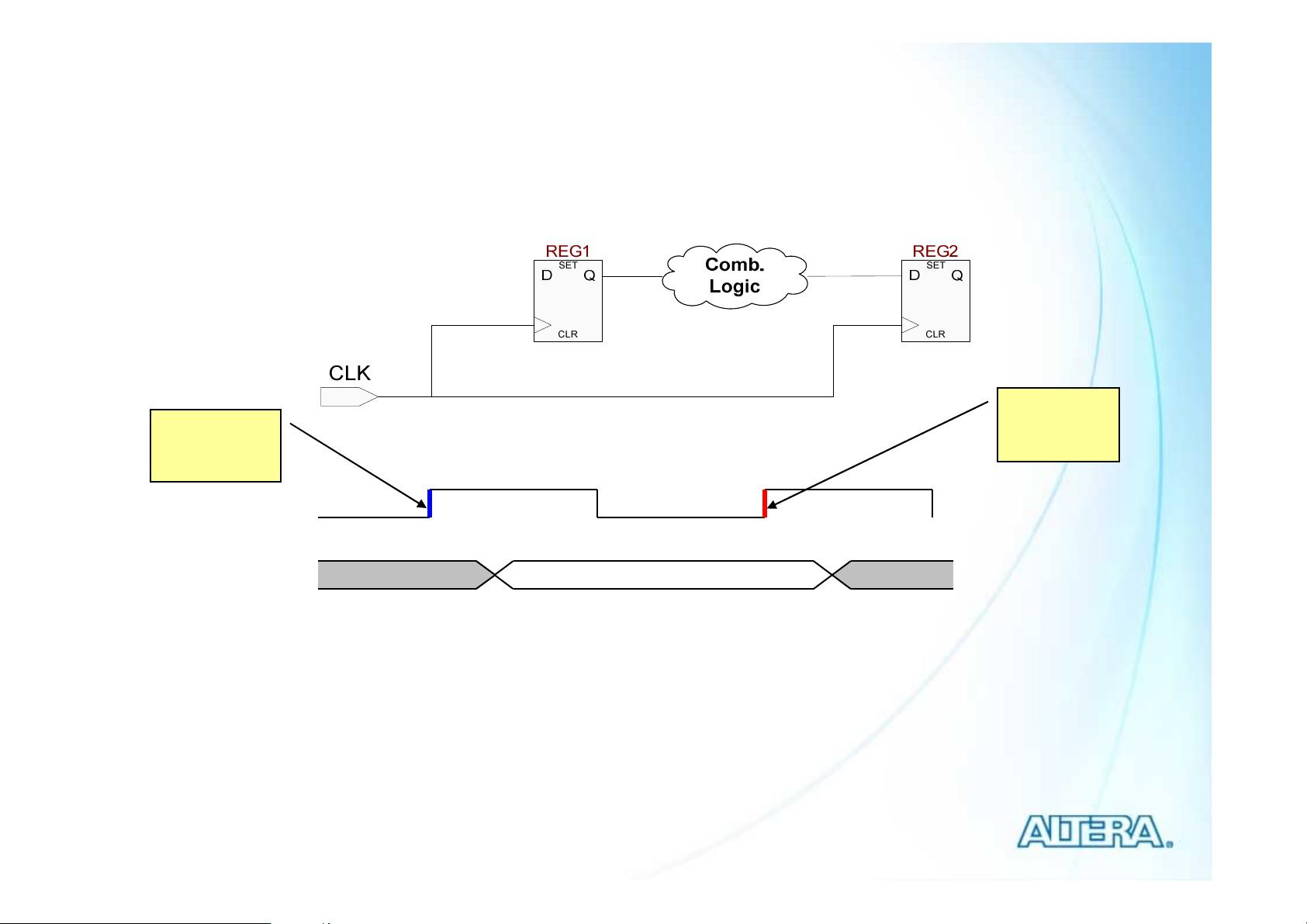

时序分析模型通常包含组合逻辑延迟和时钟路径延迟两部分。例如,图中的例子展示了带有清除(CLR)和预置(PRE)信号的D触发器,以及输入D和输出Q之间的组合逻辑延迟。时序分析不仅要考虑触发器自身的边沿延迟,还要考虑输入到触发器之间经过的组合逻辑的延迟。

在实际应用中,时序分析还包括了路径延时的计算,其中路径延时由组合逻辑延时和时钟网络延时组成。时钟网络延时是指时钟信号从源到各个时钟敏感元件的传播时间。此外,时序分析还会考虑各种边界条件和特殊情况,如电源电压变化、温度波动等因素对电路性能的影响。

总结来说,静态时序分析是数字设计中不可或缺的一部分,它通过对设计的全面检查,确保了电路在规定的时序约束下正常工作。通过理解和掌握时序分析的基本原理和Quartus® II中的时序分析工具,设计师可以更有效地优化设计,提高系统性能,降低潜在的时序故障风险。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-03-10 上传

2021-10-15 上传

2011-04-11 上传

2021-09-29 上传

2015-09-08 上传

zhiyu48

- 粉丝: 0

- 资源: 1

最新资源

- USB通信结构详细介绍

- 数据导出excel数据导出excel

- 嵌入式WEB服务器及远程测控应用详解V0.1

- 采用RF芯片组的下一代RFID阅读器.doc

- dos常用命令.txt

- Java 3D Programming.pdf

- 多读写器环境下的UHF RFID系统的抗干扰研究.doc

- Linux上安装无线网卡完美方案.doc

- 10款超值价笔记本易PC爆1499

- Jmail组件PDF文档(中文翻译)

- 移植wifi无线网卡到mini2440上全过程.doc

- ModelSim SE中Xilinx仿真库的建立

- 单片机 c语言教程 pdf

- 数据仓库技术综述 数据库

- DWR中文实例讲述文档(从基础到进阶)

- usb 1 协议中文版