下一代RFID阅读器:基于RF芯片组的创新设计

需积分: 10 29 浏览量

更新于2024-12-23

收藏 281KB DOC 举报

本文探讨了采用RF芯片组的下一代RFID阅读器的设计原理,旨在通过集成元件简化阅读器的构造,提高性能和效率。文中特别提到了不同地区的RFID阅读器的功率输出限制,以及针对这些限制采取的不同策略。此外,还分析了RFID阅读器的频率方案,源模块的设计,包括频率合成器、本振、功率分配器等方面的关键考虑因素。

在RFID阅读器的设计中,RF部分的复杂性主要源于需要处理不同地区法规对功率输出的要求。例如,美国的阅读器最大输出功率为+30dBm,欧洲为+27dBm,而日本则同样是+30dBm。根据这些规定,设计者需要选择合适的功率放大器(PA),在美国和日本,饱和功率放大器可以实现较高的功率附加效率(PAE),而在欧洲,PA需要工作在线性区,牺牲一些效率以满足带外要求。

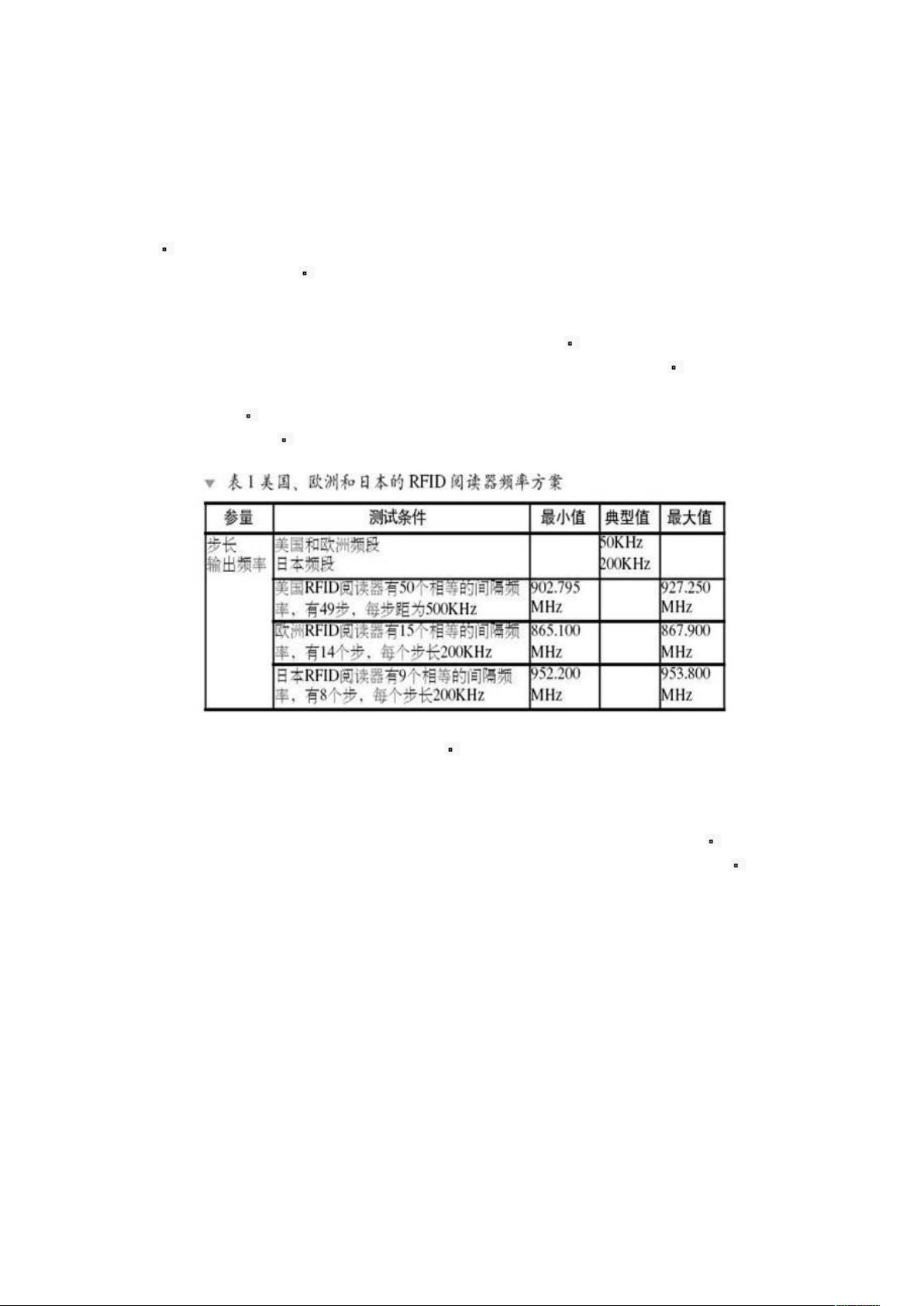

RFID阅读器的频率方案是一个重要的设计环节,表1中列出了不同的频率范围,这需要源模块能够灵活地适应各种频段。源模块的核心是频率合成器,它生成发送和接收路径所需的本地振荡器(LO)信号。为了在不同频段间切换,合成器需要配合可调谐的电压控制振荡器(VCO)和适当的电感值。此外,快速的开关速度对于在日本频段操作至关重要,这可能需要调整环形滤波器的元件值。

在源模块中,功率分配器的角色也不容忽视,它需要提供足够的隔离以避免信号干扰。对于850~960MHz的频段,可能需要采用调节电感器和电容器来优化隔离性能。为了降低成本并减小体积,各种元件如温控晶体振荡器(TCXO)和表面贴装元件(SMTI)会被集成在一起,同时还需要良好的屏蔽措施以确保环路稳定和降低相位噪声。

采用RF芯片组的下一代RFID阅读器设计涉及多个关键技术领域,包括高效功率管理、频率合成、信号隔离以及元件集成。这些技术的进步将推动RFID阅读器向着更小巧、更智能的方向发展,同时保持与全球各地法规的兼容性。通过优化这些设计要素,未来的RFID阅读器有望在读取距离、功耗和成本之间找到更好的平衡点,从而更好地服务于各种应用场合。

2020-07-31 上传

2008-10-11 上传

2022-05-10 上传

2021-10-02 上传

2021-08-22 上传

2021-09-18 上传