RISC-V无剑100 SoC异常与中断详解:E902处理器架构深入

需积分: 0 47 浏览量

更新于2024-07-01

收藏 1.49MB PDF 举报

本章节主要探讨的是基于平头哥E902处理器的SoC设计中的异常与中断管理机制,由邸志雄教授在西南交通大学授课,课程内容涵盖了RISC-V架构下的异常处理流程。RISC-V是一种开放源代码的指令集架构,其设计特点是简洁高效,异常与中断是确保系统稳定性和灵活性的关键部分。

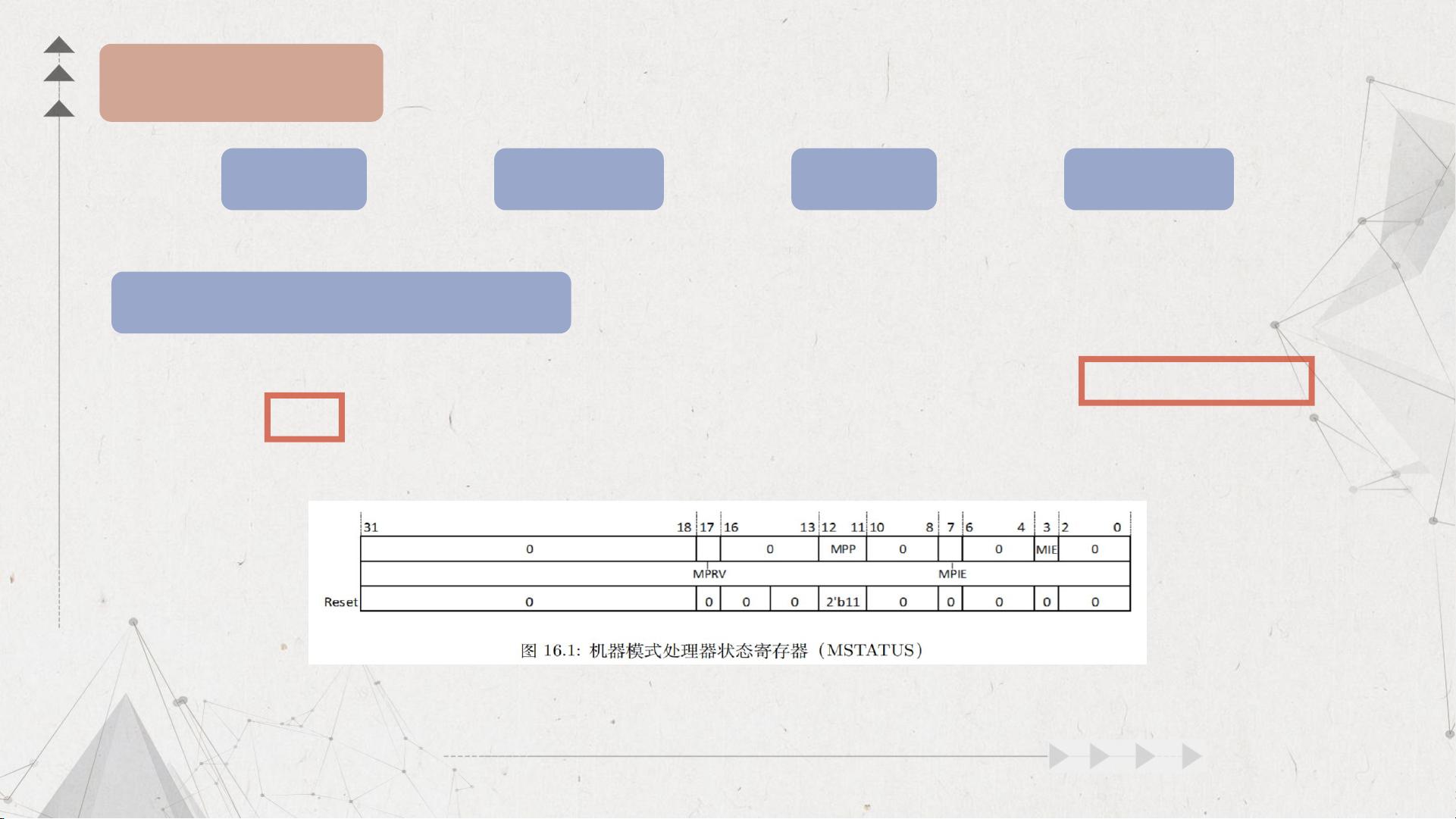

异常是指处理器在执行过程中遇到无法正常处理的情况,如非法指令、内存访问错误等,这些情况会打断当前的程序执行流程。RISC-V架构中,由于没有异常使能寄存器,一旦异常发生,处理器会立即响应。异常响应时,会更新一系列控制和状态寄存器,如机器模式异常原因寄存器mcause(记录异常类型)、机器模式异常值寄存器mtval(异常详细信息)、机器模式异常PC寄存器mepc(异常发生时的程序计数器值)以及机器模式状态寄存器mstatus(记录当前状态)。

中断则是外部硬件设备请求处理器处理特定任务的一种方式,例如I/O操作完成或定时器到期。中断通常发生在处理器执行指令的中间,需要通过中断向量表(IVT)定位相应的处理程序。在RISC-V中,中断全局开关MIE(Machine Interrupt Enable)用于控制中断是否全局开启或关闭,异常响应时会自动清零MIE,而MPIE(Machine Per-Interrupt Enable)用于记录异常发生前的中断状态,以便异常处理后恢复。

异常处理涉及从异常状态转移到异常处理程序,然后执行相应的处理逻辑。在这个过程中,异常结束后,处理器会通过mepc恢复到异常前的程序位置,但如果异常是由ecall或ebreak指令主动触发的,可能会导致死循环,这时处理程序需要更新mepc以避免无限循环。

理解并掌握异常与中断机制对于在RISC-V平台上进行高效和可靠的软件开发至关重要,包括异常的原因分析、响应流程以及中断管理,这些都是构建高性能SoC设计时不可或缺的知识点。邸志雄教授的课程提供了丰富的教学资源,包括slides和源代码,为学习者深入理解RISC-V异常与中断机制提供了详尽的指导。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-09-21 上传

2022-06-24 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

士多霹雳酱

- 粉丝: 23

- 资源: 299

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍