Verilog-XL中文操作指南:从入门到Booth乘法器设计

"Verilog-XL的中文简明操作手册"

Verilog-XL是Cadence公司为Verilog HDL提供的一款强大的仿真工具,它在电子设计自动化(EDA)领域中被广泛使用,尤其适合于数字系统的建模和验证。Verilog-HDL作为一种硬件描述语言,能够用于描述从算法级别到门级、乃至开关级别的设计抽象,因此在工业界得到了广泛应用。

1. Verilog-XL的环境设置

在使用Verilog-XL之前,首先需要确保环境配置正确。可以通过在终端输入`which verilog`命令来检查Verilog-XL是否已经安装并且可以访问。如果返回的是Verilog-XL的路径,说明安装正常;若无法访问,则需要在用户的`.cshrc`文件中添加Verilog-XL的路径,使用`setpath`命令来添加。

2. Verilog-XL的启动

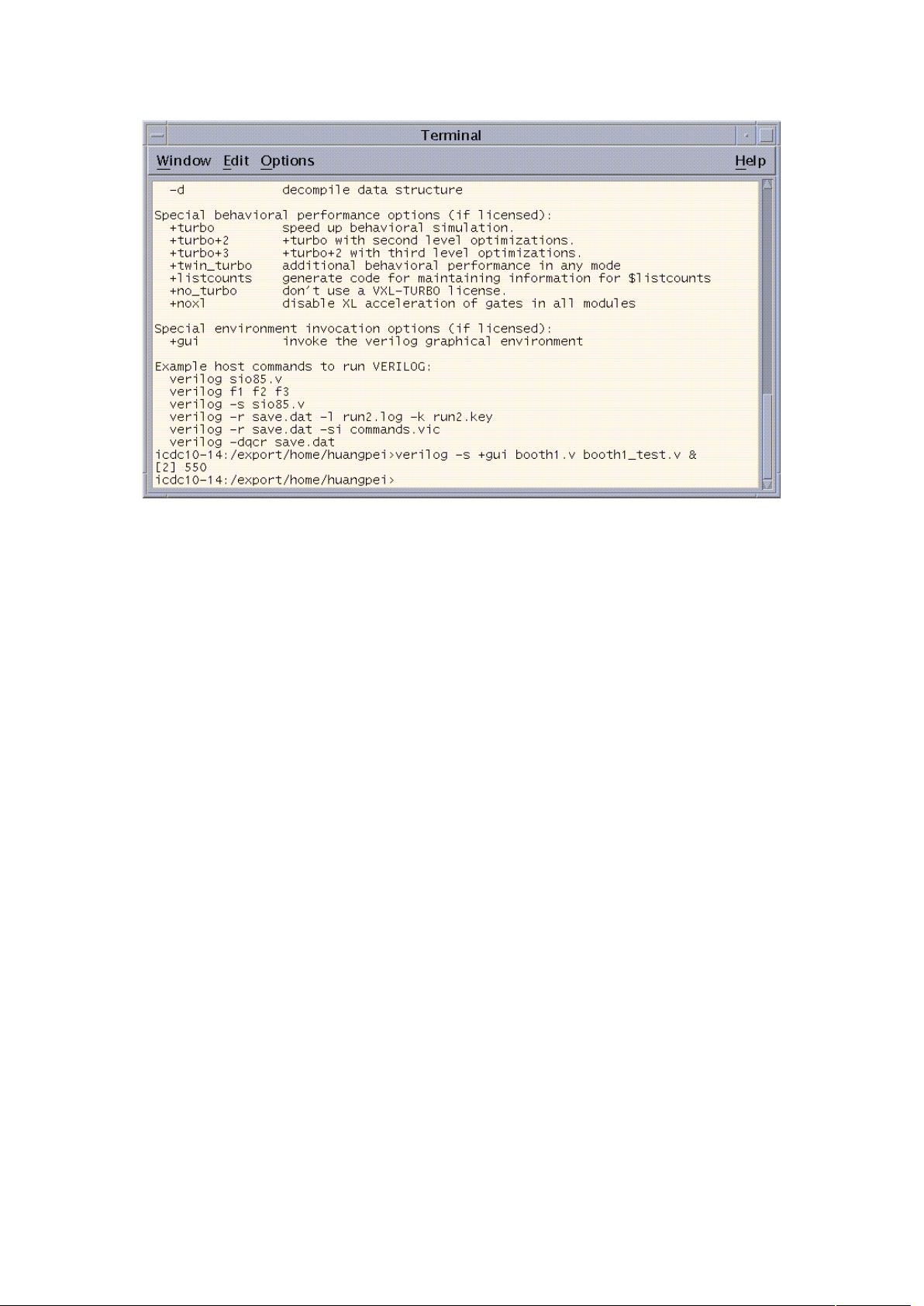

Verilog-XL的启动命令是`verilog`,并允许用户通过一系列选项自定义其行为。例如:

- `-f<filename>`:从指定文件中读取主机命令参数。

- `-v<filename>`:指定库文件。

- `-y<directory>`:指定库目录。

- `-c`:仅编译,立即进入交互模式。

- `-i<filename>`:从命令文件中输入。

- `-r<filename>`:从保存的数据结构中恢复运行。

- `-l<filename>`:设置日志文件名。

- `-k<filename>`:设置密钥文件名。

- `-u`:将标识符转换为大写。

- `-t`:启用全轨迹。

- `-q`:安静模式,减少输出信息。

- `-d`:反编译数据结构。

3. Verilog-XL的基本操作流程

这本手册通常会以一个具体的例子,如8*8位的Booth乘法器设计,来介绍如何使用Verilog-XL进行操作。基本流程包括编写Verilog代码、编译模块、创建测试平台、运行仿真以及查看和分析结果。在编写代码后,使用Verilog-XL进行编译和链接,然后通过输入命令启动仿真,观察输出波形,以验证设计的功能正确性。

4. Verilog-XL的特性与优势

Verilog-XL具有以下特点:

- 强大的编译和仿真性能,能处理复杂的系统级设计。

- 支持丰富的调试功能,如断点、变量观察等,便于问题定位。

- 提供图形化的波形显示工具,使得信号状态可视化。

- 友好的用户界面,使得操作更加便捷。

5. Verilog-HDL的编程概念

Verilog-HDL编程涉及到模块定义、并行执行、数据类型、运算符、任务和函数、时序控制、非阻塞赋值等核心概念。通过这些概念,设计者可以构建出符合实际需求的硬件模型。

6. 应用场景

Verilog-XL常用于ASIC和FPGA的设计验证,也可用于教育和研究目的,帮助设计者快速验证数字逻辑设计的正确性,减少物理实现前的错误。

总结,Verilog-XL是Cadence公司的旗舰级Verilog仿真工具,提供高效、全面的支持,使得设计者能够轻松进行Verilog HDL代码的编译、仿真和调试。通过学习这本简明操作手册,用户可以掌握使用Verilog-XL的基本步骤和技巧,从而更有效地进行数字系统设计。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-03-13 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

huangyx223

- 粉丝: 56

- 资源: 60

最新资源

- MATLAB全常用函数下载,权威性

- 基于C#的 office owc统计图解决方案

- 关于modbus学习的 pdf 文档

- 微软的面试题及答案-超变态但是很经典

- CISCO交换机配置AAA、802.1X以及VACL

- microsoft office excel 2003 函数应用完全手册

- ModBus通讯协议

- 学员信息管理系统PPT答辩稿

- D-LINK校园网设计

- 计算机三级等级考试资料

- 嵌入式C C++语言精华应用

- Java23种设计模式

- java和jsp编程常见到的异常解决方案

- Linux操作系统下C语言编程入门.pdf

- Wrox.Beginning.Shell.Scripting.Apr.2005.eBook-DDU.pdf

- 基于MVC模式Struts框架