数据选择器与D触发器结合的多输入时序电路创新设计

156 浏览量

更新于2024-08-30

收藏 236KB PDF 举报

本文主要探讨了基于数据选择器和D触发器的多输入时序电路设计,这是一种创新的时序逻辑网络结构,旨在简化电路设计过程,尤其是在处理多输入变量时序逻辑网络时。设计的核心思想是结合D触发器的存储功能和数据选择器的数据选择能力,构建既能保存状态又能根据输入进行动态数据选择的系统。

在传统的SSI(小规模集成电路)时序逻辑电路设计中,设计师追求的是最小化触发器的激励函数,以减少电路复杂性。然而,对于多输入变量,利用卡诺图或公式法进行函数化简往往变得复杂且困难。因此,作者提出了一种新的设计策略,通过一个D触发器和一个数据选择器的基本单元构建时序网络,使得电路结构更为直观和简洁。

具体设计步骤如下:

1. **基本原理**

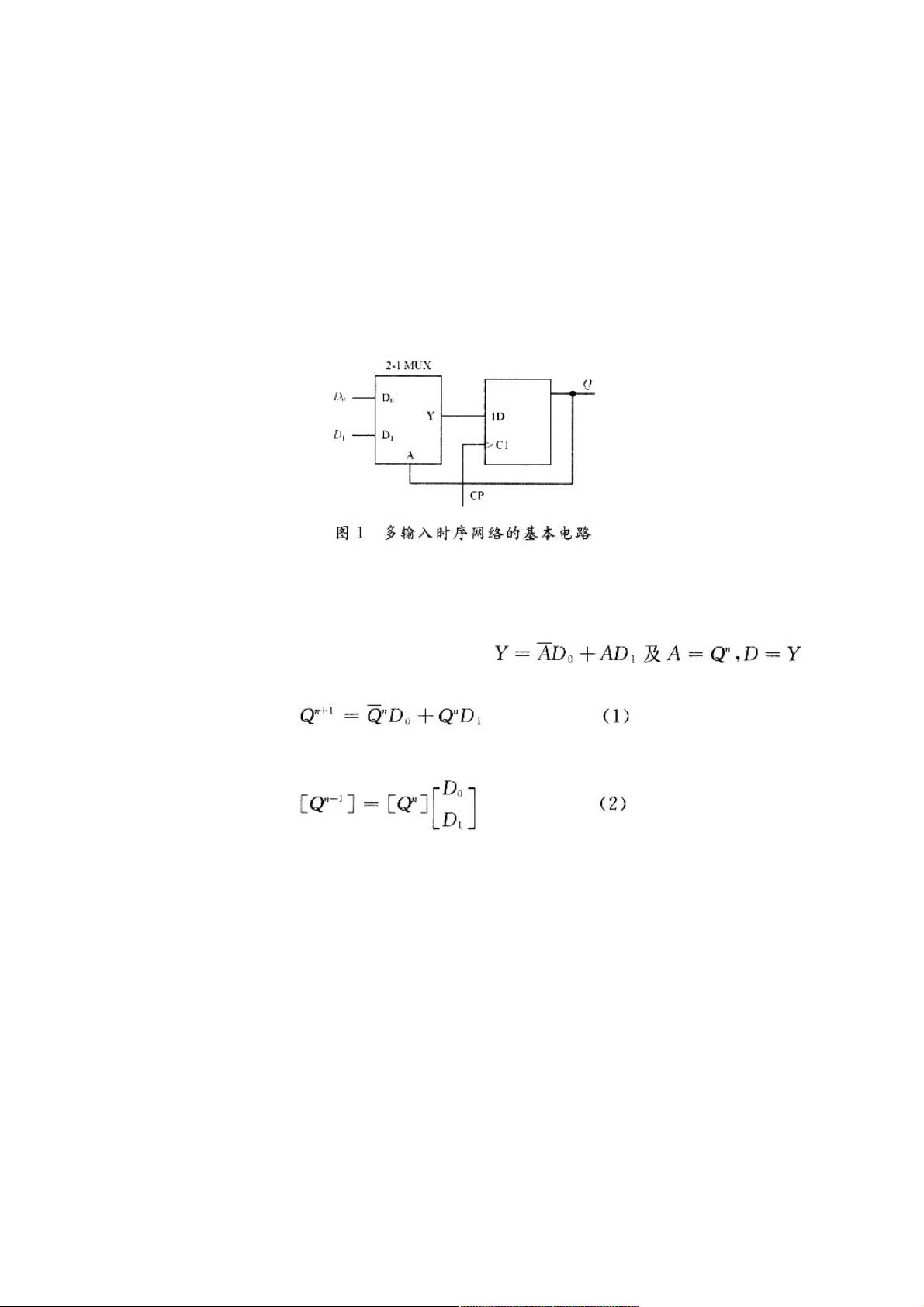

- **多输入时序网络的基本形式**:由一个D触发器和一个2选1数据选择器组成,其中触发器的当前输出Qn作为选择器的输入,选择器的输出决定触发器的下一次状态,而数据选择器的输入端则作为外部信号输入。

- **状态方程**:通过触发器的特性方程和数据选择器的逻辑表达式,可以建立多输入时序网络的状态转移方程,用矩阵形式表示。

- **输入矩阵参数确定**:根据给定的状态转换关系,通过设置D输入值来确定输入矩阵,确保正确的状态转换。

2. **扩展到2个状态变量的网络**:

- **网络结构**:使用两个D触发器和两个4选1数据选择器,每个触发器的两个输出作为选择器的选择输入,选择器的输出驱动相应触发器的D输入,输入端则有多个选项供选择。

这种设计方法的优势在于它避免了繁琐的函数化简步骤,直接通过状态转换关系和选择器来控制触发器的状态,使得电路设计更加直观且易于实现。对于那些需要处理大量输入或复杂状态转移的时序逻辑应用,这种方法无疑提供了一个高效和易于理解的解决方案。在SoPC(可编程系统级芯片)领域,这样的设计技术具有很高的实用价值,因为它能够有效降低硬件实现的复杂性和成本。

920 浏览量

157 浏览量

461 浏览量

2024-04-28 上传

153 浏览量

399 浏览量

点击了解资源详情

172 浏览量

157 浏览量

不善言辞的我

- 粉丝: 258

- 资源: 920

最新资源

- 电子功用-方形电池侧焊夹具

- 基于NB-IoT的温室大棚环境监测系统 农业大棚监测控制系统 智慧农业(使用STM32开发板,仅电子资料)

- 禅道项目管理软件ZenTaoPMS v12.5.1

- 机器学习中的公平性【卡内基梅隆大学-CMU】.zip

- jQuery-Slider:完成了自定义jQuery滑块的集成,以集成到Omni-Update的TTUISD的OU校园CMS中

- 云

- Windows Communication Foundation 和 Builder NE 类型安全 API:“MATLAB 艺术”帖子的代码 - 如何使用 Builder NE 构建 Web 服务。-matlab开发

- اصالت سنج نماد اعتماد الکترونیکی-crx插件

- IPA-Ablage:IPA Dies ist eine weitere Ablagefürdie Dokumente von meiner

- 购买电视剧版权合约书

- keil MDK仿Vscode主题配色

- 毕业设计选题系统

- jetbrains-academy:JetBrains学院解决方案

- roms:光盘

- HSP

- ECG_Viewer:Matlab GUI,用于检查,处理和注释心电图(ECG)数据文件