D触发器与数据选择器结合的多输入时序电路设计

158 浏览量

更新于2024-08-30

收藏 224KB PDF 举报

"基于数据选择器和D触发器的多输入时序电路设计"

在电子工程领域,时序逻辑电路设计是构建数字系统的核心部分。传统的SSI(Small-Scale Integration)时序逻辑电路设计通常需要通过复杂的函数化简来优化触发器的激励函数,以简化电路结构并确保其正确功能。然而,当涉及多个输入变量时,这种方法变得极其繁琐且不实用。为了解决这一问题,一种新的设计策略被提出,即利用数据选择器和D触发器的组合来构建多输入时序网络。

1. 基本原理

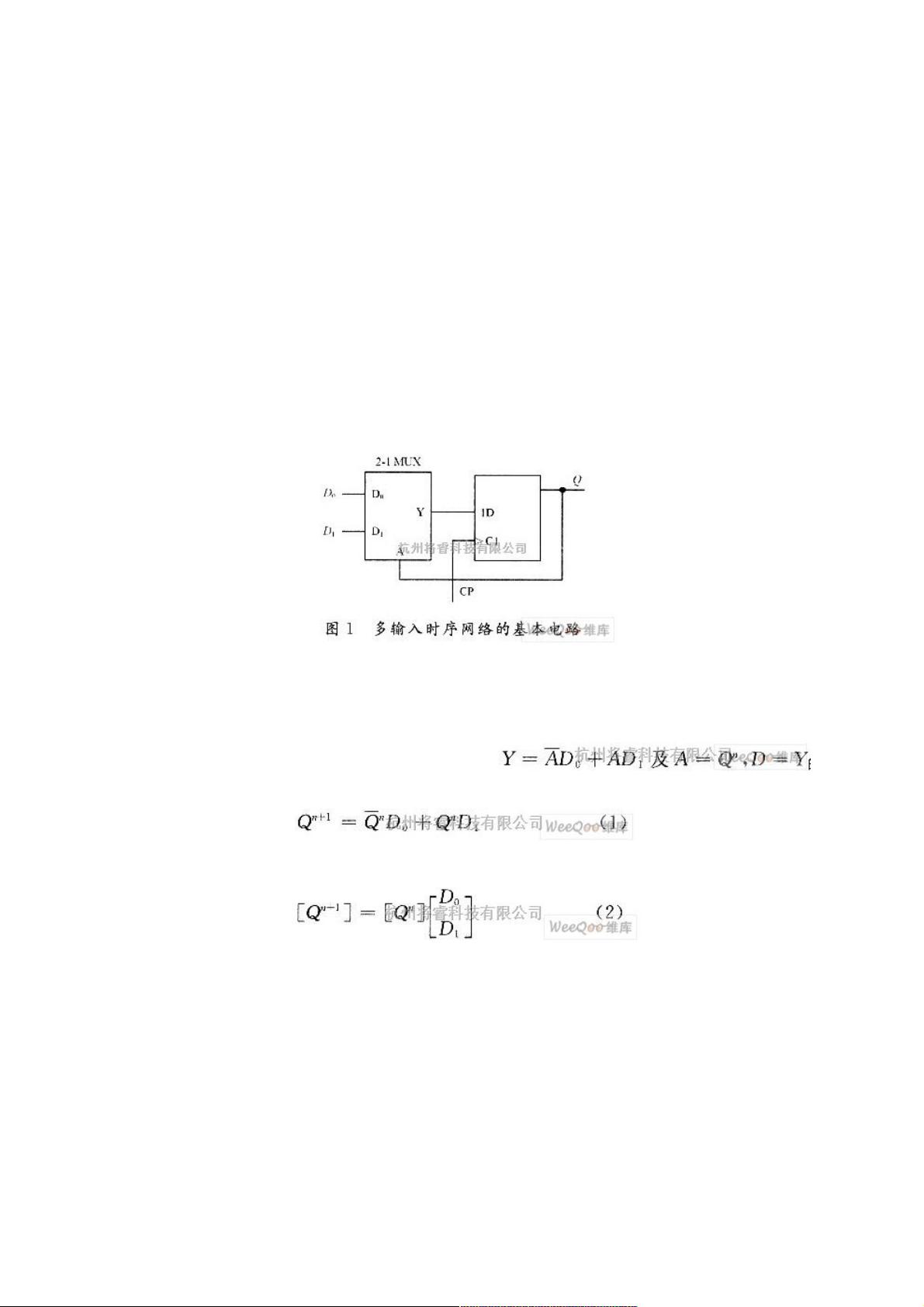

该方法的基础是结合D触发器的存储功能和数据选择器的数据选择功能。D触发器是一种常见的边沿触发的时序元件,其输出状态Qn+1在时钟脉冲的上升沿更新为输入D。而数据选择器则可以依据选择输入信号选取不同的数据源输出。在一个基本的多输入时序网络中,D触发器的现态Qn作为数据选择器的选择输入,数据选择器的输出Y则作为D触发器的输入D,这样就形成了一个既可以存储信息又可以根据外部信号动态选择输入的电路。

1.1 基本多输入时序网络

1.1.1 基本电路结构

一个简单的多输入时序网络由一个D触发器和一个2选1数据选择器构成。数据选择器的两个输入D0和D1接收到外部信号,其选择输入由触发器的现态Qn决定。当Qn=0时,数据选择器选择D0作为输出,反之,当Qn=1时,选择D1。

1.1.2 状态方程

这个网络的状态方程可以通过D触发器的特性方程Qn+1=D和数据选择器的输出逻辑表达式推导得出。结合这两个方程,我们可以得到一个多输入时序网络的状态转换矩阵。

1.1.3 设计过程

设计多输入时序网络的关键在于确定输入矩阵参数,这取决于预期的状态转换。例如,当现态Qn=0时,为了实现0→0或0→1的状态转换,需要相应地设置D0;同样,当现态Qn=1时,通过设定D1可以实现1→0或1→1的状态转换。

这种设计方法的优势在于,它允许设计者直接根据所需的逻辑状态转换关系来配置输入矩阵,而不必进行复杂的函数化简。这大大简化了多输入时序电路的设计流程,提高了设计效率,并降低了出错的可能性。

总结来说,"基于数据选择器和D触发器的多输入时序电路设计"提供了一种创新的设计策略,通过集成这两种组件,能够高效地构造复杂时序逻辑电路,同时避免了传统设计中繁琐的函数化简步骤。这种方法对于现代数字系统的快速开发和优化具有重要的实际意义。

922 浏览量

158 浏览量

204 浏览量

2024-04-28 上传

154 浏览量

401 浏览量

2021-11-05 上传

点击了解资源详情

173 浏览量

weixin_38692043

- 粉丝: 9

最新资源

- 易语言实现百度短网址的POST方法

- Lyo:轻松实现Node.js模块到浏览器的转换

- Upptime监控页面:开源正常运行时间监控与状态

- SpringBoot整合响应式框架实现高并发Web应用开发教程

- Python nbimporter:弃用从IPython笔记本导入模块的实践

- CS331课程实践:掌握数据结构和算法

- 单片机LED显示用字库文件压缩包解析

- 易语言实现淘宝邮箱批量绑定自动化操作指南

- C#练习项目集:提升编程技能

- C# 实现Windows定时服务的创建与发布指南

- MATLAB软件包助力光学镜头SFR计算

- 数学建模在自来水管系统中的应用代码解析

- 开源数字命理计算器:Mac OS X 上的生活信息解析

- 当当网JS焦点图广告代码实现与解析

- 易语言实现UDP内网P2P交互技术详解

- 易语言BE5.0游侠源码深度解析与应用