重庆大学2019数字逻辑期末试题详解:填空、逻辑设计与Verilog编程

需积分: 0 179 浏览量

更新于2024-08-03

1

收藏 1.17MB PDF 举报

重庆大学计算机学院2019年数字逻辑期末试题涵盖了多个核心知识点,旨在检验学生对基础理论的理解和实践能力。以下是详细的解析:

1. **八进制与二进制转换** - 本部分考察了基本的数字系统转换技巧,包括八进制数(10001101)转换为二进制的原码和补码。对于正数,原码、补码和反码是一致的;负数则需要考虑符号位的处理和补码的计算方法。

2. **逻辑运算** - 包括与(AND)、或(OR)和非(NOT)三个基本逻辑操作,理解它们的运算是组合逻辑的基础。

3. **竞争和冒险问题** - 组合逻辑电路中的竞争和冒险现象是电路设计时需要避免的问题,指的是因电路结构导致的信号不确定性和可能的错误输出。

4. **卡诺图** - 题目提到卡诺图的逻辑相邻概念,指的是在卡诺图中,两个最小项之间的关系只有当它们的某一位不同时才表示逻辑上相连。

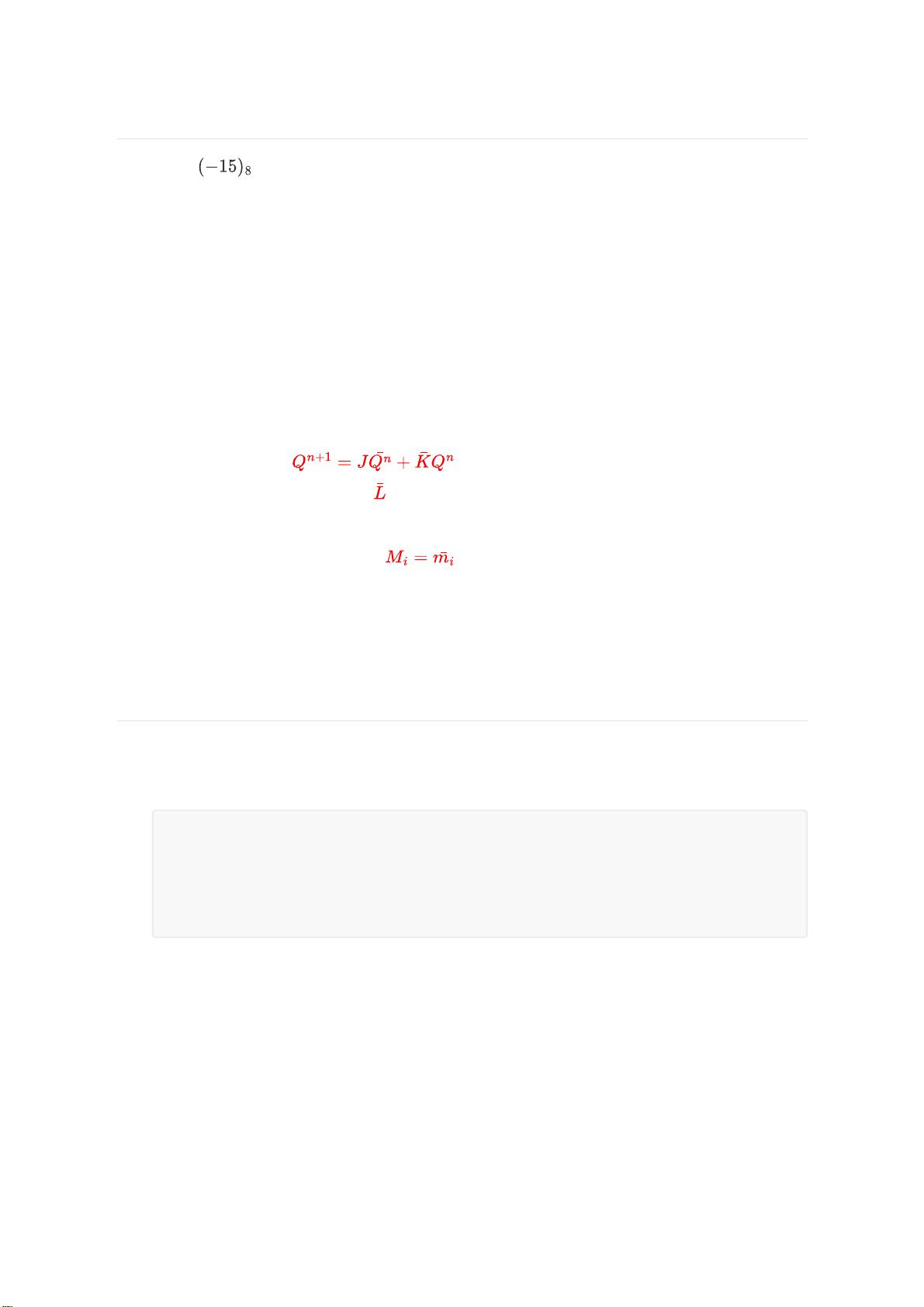

5. **JK触发器特性方程** - JK触发器是一种双稳态触发器,其特性方程包含了J、K输入信号对触发状态的影响。

6. **函数对偶** - 提及到的可能是逻辑函数的对偶,即通过改变原函数中变量的“与”、“或”关系来得到新的逻辑函数,常用于简化逻辑设计。

7. **电路类型区分** - 译码器通常被设计为组合逻辑电路,因为它不依赖于之前的状态,而只基于当前输入立即产生输出。

8. **最大项和最小项的关系** - 最大项和最小项之间存在互补关系,即一个最大项的取反结果为对应的最小项。

9. **时间尺度定义** - `timescale5ns/1ps` 表示时间间隔的单位为5纳秒,时间精度为1皮秒,这对于时序电路的设计至关重要。

10. **Verilog程序结构** - 包括模块声明、端口定义、信号类型声明以及功能描述,这是硬件描述语言中编写模块的基本组成部分。

11. **同步与非同步逻辑设计** - 通过代码展示了非阻塞赋值和阻塞赋值的区别,以及如何在Verilog中对应地绘制时序图。

12. **逻辑设计与分析** - 分析题涉及卡诺图化简和逻辑电路设计,如用卡诺图简化给定函数为最简与或表达式,并实现对应的逻辑电路。

13. **计数器设计** - 实现了一个四位计数器模块,包含输入信号如时钟、清零、加载和使能,以及输出信号如当前值和进位信号,涉及到同步时序逻辑的设计。

总结来说,这份试题涵盖了数字逻辑的基本理论(如数制转换、逻辑运算和触发器),电路设计原则(竞争冒险、卡诺图),以及硬件描述语言的使用,同时考验了学生对于同步与非同步逻辑、时序电路设计以及基本逻辑门级设计的实际操作能力。

372 浏览量

435 浏览量

764 浏览量

146 浏览量

479 浏览量

191 浏览量

1376 浏览量

219 浏览量

Haru_Yuki

- 粉丝: 240

- 资源: 1

最新资源

- DFSBack:DFS站点管理系统

- docker-tutorial:零基础学习docker,从应用入手带你深入理解docker

- 易语言学习-高级表格支持库最新测试版(2012-11-2).zip

- appfuse-service-3.0.0.zip

- 精益求精上网导航精美版生成htmlV090308

- ScoketServer.7z

- 参考正点原子,二次改造的STM32板卡原理图分享-电路方案

- Accelerated C# 2010.rar

- AcidPlatformer:这是一个简单的javascript平台程序,可能会随着时间的推移而演变为更多东西

- apm-agent-python:弹性APM的官方Python代理

- eshop-cache.rar

- studentManage.zip

- Module-6-Assessment-2

- :laptop:功能齐全的本地AWS云堆栈。 离线开发和测试您的云和无服务器应用程序!-Python开发

- 一组经典小图标 .xd .sketch .fig .png .svg素材下载

- django-accounting:适用于Django 1.7+项目的计费可插拔应用