Verilog实现乘法器:移位、原码、补码及流水线

需积分: 0 77 浏览量

更新于2024-08-04

收藏 250KB DOCX 举报

"这篇文档是关于使用Verilog语言设计乘法器的教程,具体包括了移位乘法器、原码乘法器、补码乘法器和流水线乘法器四种类型的乘法器设计。其中,给出了一个左移位乘法器的详细设计实例,并提供了对应的仿真文件以验证设计的正确性。"

在Verilog硬件描述语言中,乘法器的设计是一项基本任务,它广泛应用于数字逻辑系统和集成电路设计中。文档中首先提到了几种常见的乘法器类型:

1. **移位乘法器**:这种乘法器利用二进制数的移位操作来实现乘法。例如,左移位乘法器通过将一个操作数左移指定次数来完成乘以另一个操作数(通常是2的幂)的计算。

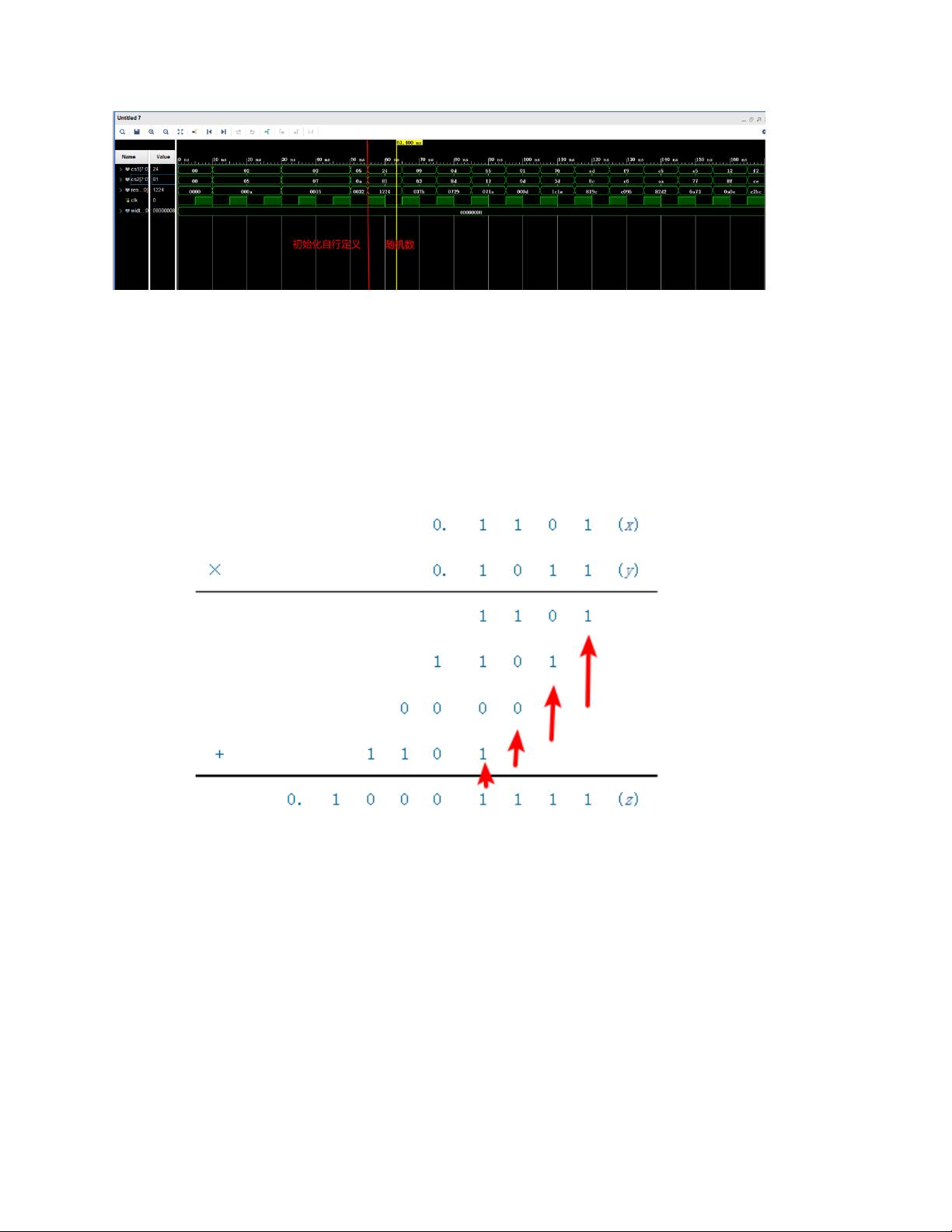

在提供的设计文件中,`cfq`模块展示了如何用Verilog实现一个左移位乘法器。该模块有三个参数:`result`是乘法结果,`a`和`b`分别是两个输入操作数。在设计中,`result`被初始化为0,然后通过一个for循环逐位进行乘法操作。如果`b[index]`为1,则将`a`左移`(index-1)`位并累加到`result`上。

2. **仿真文件**:为了验证设计的正确性,文档还提供了一个名为`cfqsimu`的仿真模块。这个模块创建了输入信号`a`和`b`,以及输出`result`,并使用`initial`块来设置初始值和自增逻辑。然而,文档指出这种简单的自增逻辑在正确性表现上可能不直观。

为了解决这个问题,文档建议使用另一种Testbench方法,即预先定义多组测试数据,并在每个时钟周期生成随机数来更全面地验证乘法器的功能。在改进后的`cfqsimu`模块中,引入了一个时钟信号`clk`,并使用`repeat`和`posedge`语句来在每个时钟边沿生成随机输入,使得波形图的显示更加直观。

3. **原码乘法器和补码乘法器**:这两种乘法器主要用于处理有符号整数的乘法。原码乘法器直接对操作数的原码进行运算,而补码乘法器则先将操作数转换为补码形式再进行运算,以处理负数的情况。虽然文档没有详细展开,但通常它们会涉及到溢出检测和符号位的处理。

4. **流水线乘法器**:流水线技术用于提高乘法器的运算速度,它将乘法过程分解为多个阶段,每个阶段在不同的时钟周期内完成,从而实现了并行计算的部分。

这个文档提供了一个基础的Verilog乘法器设计实例,以及对不同类型的乘法器的简要介绍,对于学习Verilog和数字逻辑设计的初学者来说是一份有价值的参考资料。在实际应用中,设计者可以根据需求选择合适的乘法器结构,并结合仿真和测试来确保设计的正确性和性能。

2021-10-03 上传

136 浏览量

2020-04-20 上传

2021-10-04 上传

2022-07-13 上传

2022-07-15 上传

2021-10-10 上传

2022-09-21 上传

2022-09-24 上传

胡说先森

- 粉丝: 711

- 资源: 280

最新资源

- 教你怎么写批处理.txt

- C语言 描述 数据采集 程序

- Oracle9i 数据库管理基础 I Ed 1.1 Vol.1

- intel平台的ELF 文件格式

- High.Performance.MySQL_Second.Edition.pdf

- 基于_NET企业信息资源管理系统的设计与实现

- Linux操作系统编程入门

- Ethereal用户手册.pdf

- 基于UDP通信协议的设计与实现

- 红外遥控系统原理及单片机软件解码实例

- 三言两语话Erlang

- java编程入门知识

- NET SQL Server数据访问抽象基础类

- linux 菜鸟过关

- Android 入门教程

- Oracle+9i&10g编程艺术:深入数据库体系结构