FPGA加速器:Xilinx SDAccel 提升数据中心能效性能

38 浏览量

更新于2024-09-01

收藏 502KB PDF 举报

“Xilinx SDAccel 环境提供了为数据中心优化的硬件加速解决方案,旨在解决CPU和GPU在单位功耗性能上的局限性。该环境使得设计人员能够利用FPGA(现场可编程门阵列)的优势,实现低功耗、高吞吐量和低时延,特别适用于大规模数据中心应用,如密钥加速、图像识别、语音转录等。”

赛灵思SDAccel环境是针对数据中心应用开发的一款创新工具,它解决了当前多核CPU和GPU在性能与功耗之间平衡的挑战。传统的CPU和GPU虽然易编程,但在处理密集型任务时,功耗与性能的比例限制了其潜力。设计人员对硬件加速器的需求日益增长,他们期望既能保持GPU的易编程性,又能拥有更低功耗、更高效率的硬件。

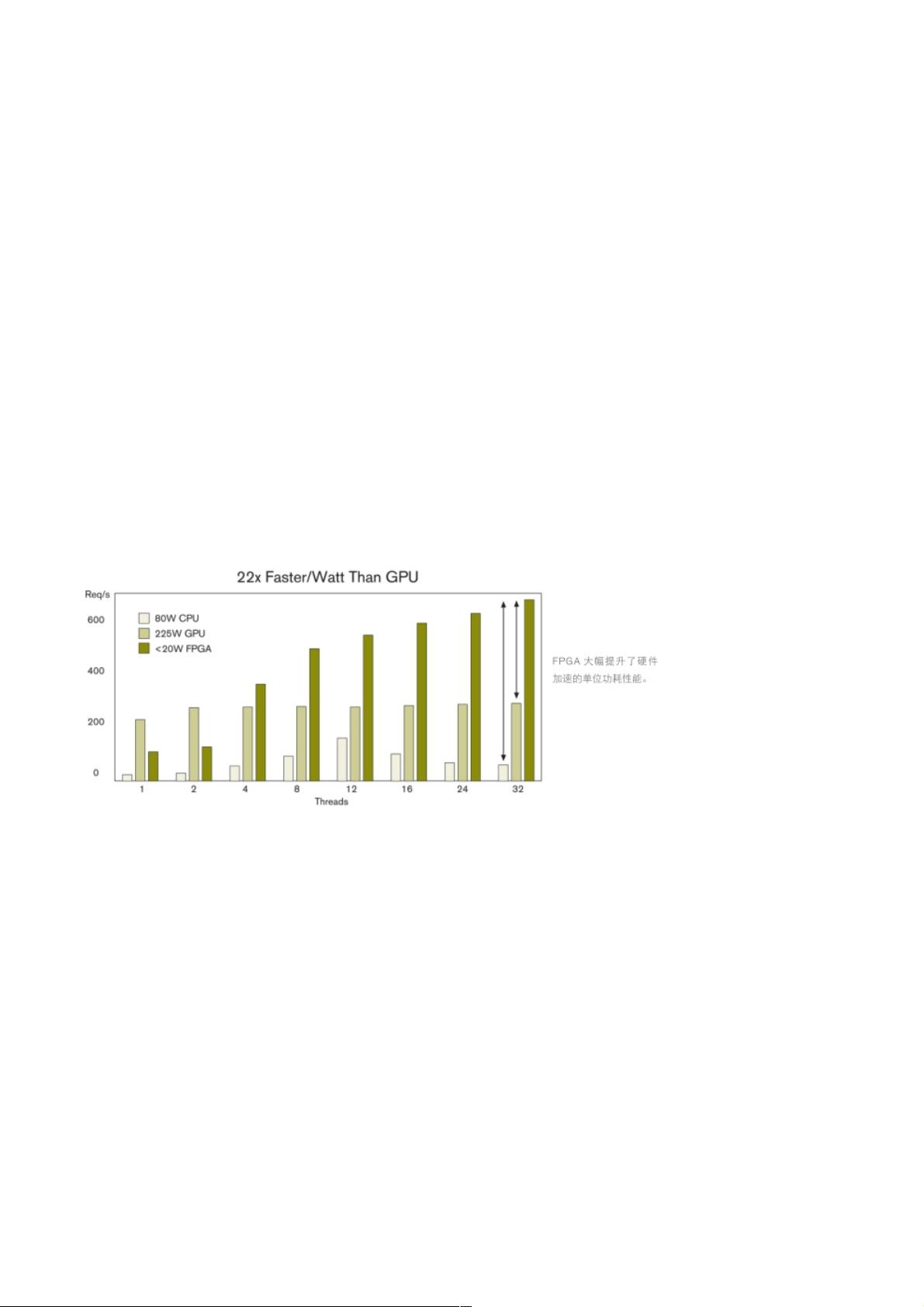

FPGA作为一种灵活的硬件平台,可以在单位功耗性能上提供显著提升。研究表明,基于FPGA的应用加速相比于CPU和GPU,可以实现25倍的能效提升和50到75倍的时延减少。这种高效性能的实现部分得益于FPGA对I/O集成的支持,如PCIe、DDR4 SDRAM接口和高速以太网等。此外,FPGA还能满足25W以下的目标功耗,从而提高可扩展性和降低总体功耗。

以百度为例,该公司展示了FPGA在深度神经网络(DNN)预测系统中的优势,DNN广泛应用于语言识别、图像搜索等多个领域。FPGA的低功耗特性使得它们成为所有类型服务器的理想加速器,尤其在中端应用中,可以实现375GFLOPS的性能,功耗仅在10-20W之间。

为了解决FPGA编程的难题,赛灵思推出了SDAccel环境。这个全新的开发环境为数据中心应用开发人员提供了以下关键功能:

1. **更高的单位功耗性能**:SDAccel允许利用FPGA的硬件加速能力,以更低的功耗实现更高效的计算。

2. **完全软件的开发环境**:不同于传统的硬件描述语言(RTL)流程,SDAccel支持软件开发者熟悉的编程模型,如OpenCL、C和C++,降低了编程难度。

3. **易于升级的设计**:SDAccel环境支持设计的平滑迭代和升级,使开发人员能够快速适应不断变化的技术需求。

Xilinx SDAccel环境为数据中心应用开发带来了一场革命,通过结合FPGA的灵活性和软件友好性,为寻求高性能、低功耗解决方案的数据中心提供了理想选择。这一工具不仅提升了硬件加速的易用性,还推动了数据中心技术在能效和性能上的新突破。

116 浏览量

128 浏览量

102 浏览量

638 浏览量

2021-07-13 上传

2020-08-02 上传

点击了解资源详情

点击了解资源详情

110 浏览量

weixin_38506798

- 粉丝: 4

最新资源

- Saber仿真下的简化Buck环路分析与TDsa扫频

- Spring框架下使用FreeMarker发邮件实例解析

- Cocos2d捕鱼达人路线编辑器开发指南

- 深入解析CSS Flex布局与特性的应用

- 小学生加减法题库自动生成软件介绍

- JS颜色选择器示例:跨浏览器兼容性

- ios-fingerprinter:自动化匹配iOS配置文件与.p12证书

- 掌握移动Web前端高效开发技术要点

- 解决VS中OpenGL程序缺失GL/glut.h文件问题

- 快速掌握POI技术,轻松编辑Excel文件

- 实用ASCII码转换工具:轻松实现数制转换与查询

- Oracle ODBC补丁解决数据源配置问题

- C#集成连接器的开发与应用

- 电子书制作教程:你的文档整理助手

- OpenStack计费监控:使用collectd插件收集统计信息

- 深入理解SQL Server 2008 Reporting Services