HDB3编码器ASIC设计在单片机与DSP中的应用

77 浏览量

更新于2024-09-01

收藏 236KB PDF 举报

"单片机与DSP中的HDB3编码器ASIC设计主要关注的是在数字通信领域如何利用专用集成电路实现高效、稳定的基带信号传输。HDB3码(High Density Bipolar with 3 consecutive zeros,高密度双极性码,带有三个连续零的修正码)在基带信号传输系统中扮演着重要角色,因为它继承了AMI码(Alternate Mark Inversion,交替标记反相码)的优点,可以消除直流成分和低频成分,确保信号的纯净传输。

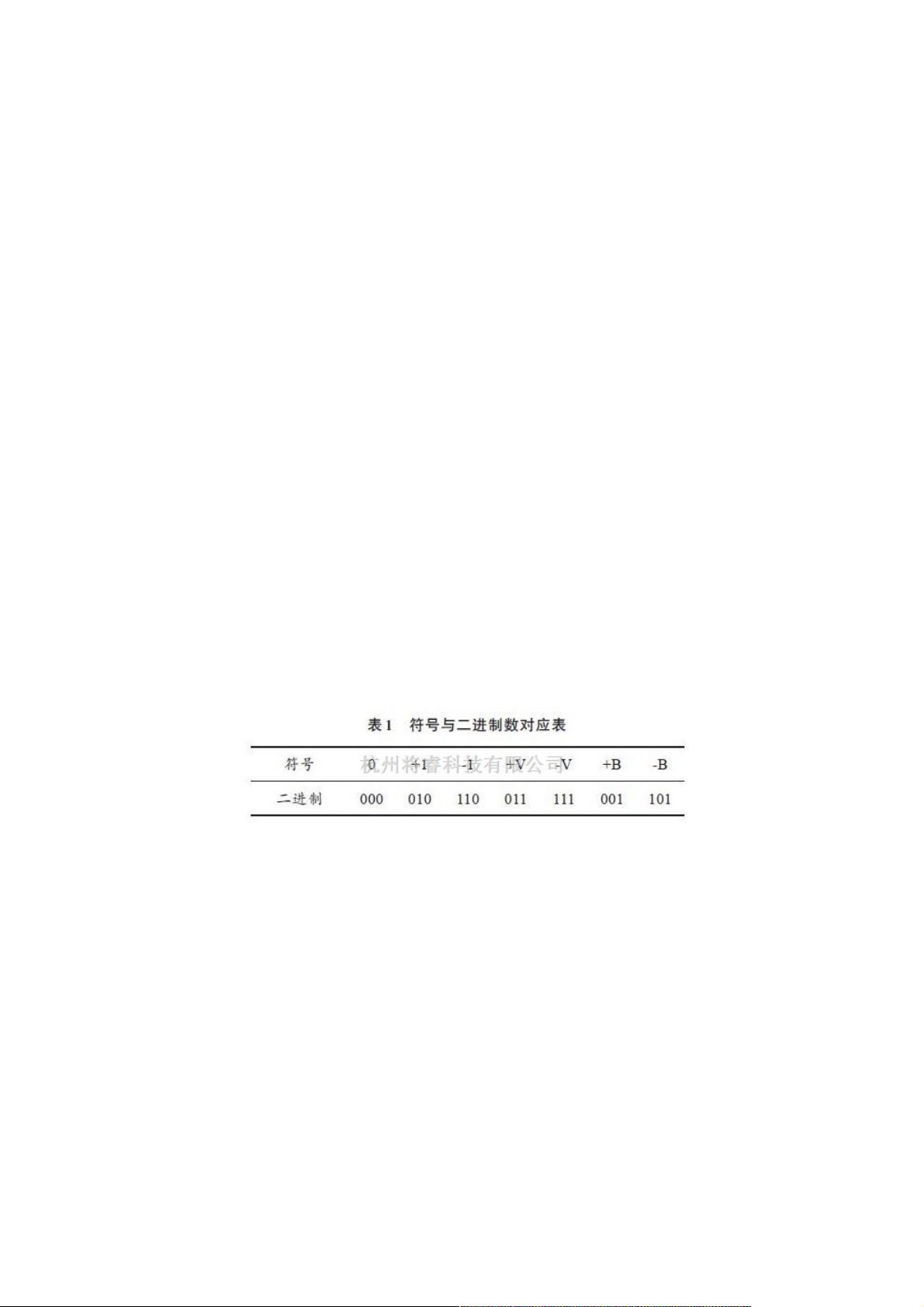

HDB3编码器ASIC设计的关键在于集成插“V”、插“B”和“V”码极性纠正模块。这些模块的作用是在出现连续四个及以上“0”的地方插入“B”码(正或负1),以避免连续的零出现,同时对“V”码的极性进行纠正,保持码型的平衡。这样的设计有助于消除信号中的直流偏移,防止信道中的低频成分干扰,从而提高传输质量。通过仿真和硬件验证,可以确保编码器在实际应用中能够有效地处理信号,提供可靠的基带信号传输和定时信号提取。

在数字通信系统中,基带调制是发送端的核心任务,即将数字信号转化为适合信道传输的基带信号。而接收端则执行基带解调,将接收到的基带信号恢复为原始数字信号。选择合适的码型是确保这一过程准确无误的关键。HDB3码由于其易于提取定时信号、无直流成分和低频成分、高传输效率的特性,成为基带信道传输的理想选择。

设计HDB3编码器ASIC的过程通常包括以下步骤:首先,使用硬件描述语言如Verilog HDL进行前端逻辑设计,并在如Quartus II这样的工具上进行编译和仿真;接着是综合阶段,将逻辑设计转换为门级电路;随后进行门电路仿真和硬件验证,以确保设计功能的正确性;最后,进行后端版图设计,优化物理布局,以满足芯片尺寸、功耗和速度的要求。

HDB3编码器的硬件描述语言设计需要考虑编码的逻辑流程,即从输入的AMI码检测连续“0”,插入“B”码,以及在适当位置调整“V”码的极性。这个设计过程涉及到状态机的构建,通过状态转移来实现编码规则,确保每个步骤都能准确无误地执行,从而生成符合HDB3码规范的输出。

单片机与DSP中的HDB3编码器ASIC设计是一项至关重要的技术,它直接影响到数字通信系统的性能和稳定性。通过精心设计的ASIC,可以实现高效的数据传输,减少信号失真,提升通信系统的整体性能。

2020-07-06 上传

2020-07-21 上传

2009-06-10 上传

2022-09-20 上传

点击了解资源详情

点击了解资源详情

2021-01-19 上传

2020-11-12 上传

weixin_38707240

- 粉丝: 5

- 资源: 921

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器