HDB3编码器ASIC设计与优化

130 浏览量

更新于2024-08-28

收藏 301KB PDF 举报

"HDB3编码器ASIC的设计"

在数字通信技术中,HDB3编码(High Density Bipolar with 3 consecutive zeros, 高密度双极性码,允许连续三个零)是一种广泛应用于基带信号传输的码型。这种编码方式在保持AMI(Alternating Mark Inversion,交替标记反转码)优点的同时,还能够有效地处理和优化信号传输过程中的关键问题。HDB3编码器是实现这一功能的核心组件,通常采用ASIC(Application-Specific Integrated Circuit,专用集成电路)形式设计,以满足通信系统高效稳定运行的需求。

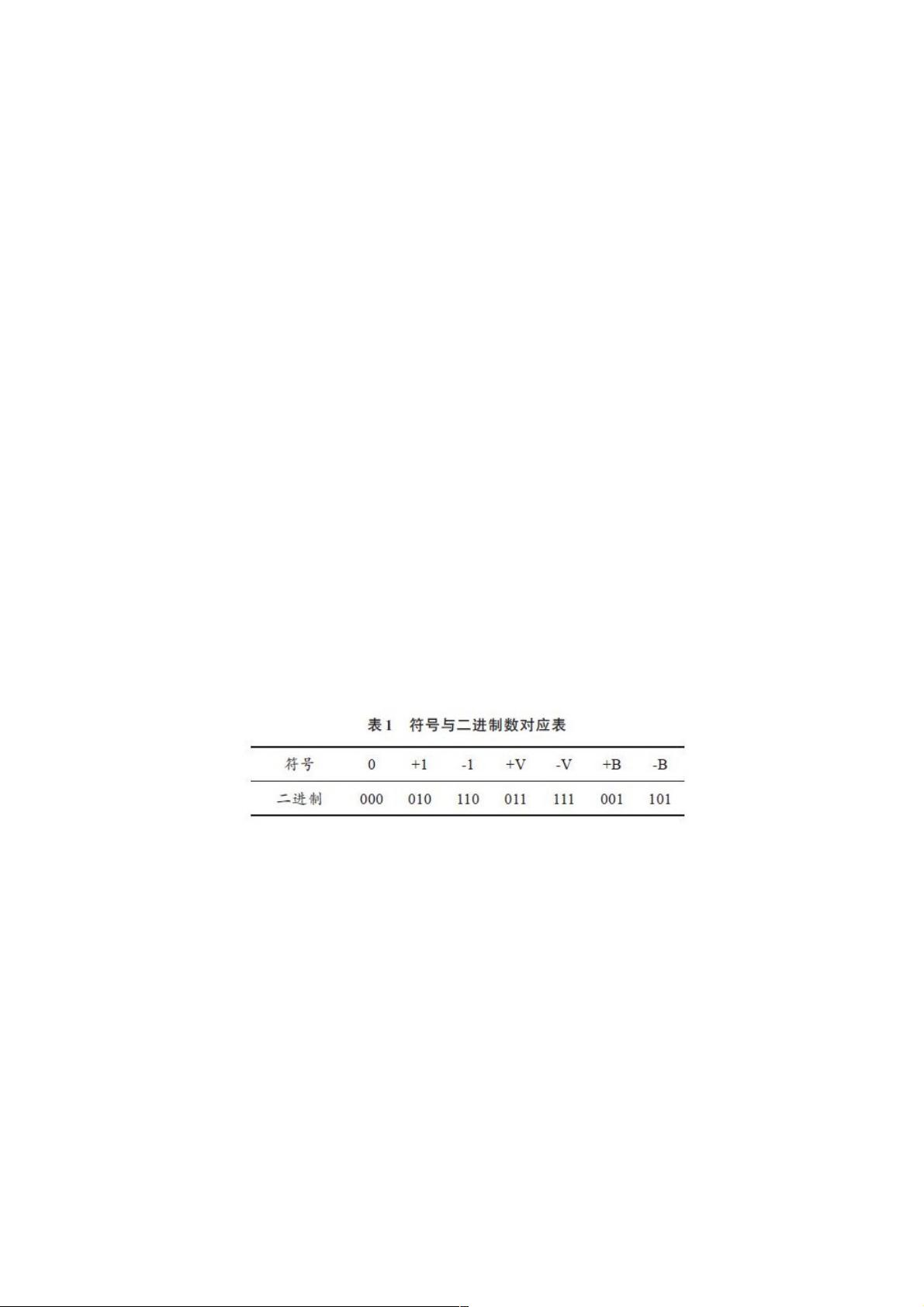

HDB3编码器ASIC集成了插“V”,插“B”以及“V”码极性纠正模块,这些模块的主要任务是防止连续三个零的出现。当检测到连续三个零时,“V”码(+1或-1)会被插入,以保持码型的平衡特性。此外,该编码器还包括极性纠正功能,用于确保信号中的直流偏移和低频成分得到消除,这有利于基带信号在传输过程中保持高质量,避免信号失真和干扰。

在数字通信系统中,发送端首先通过基带调制将数字信号转换为适合信道传输的基带信号,然后通过信道发送。接收端再进行基带解调,将接收到的基带信号恢复为原始的数字信号。码型选择对于整个通信系统的性能至关重要,HDB3码由于其独特的优点,如易于提取定时信号、没有直流分量和低频成分,以及高效的传输效率,成为了基带信道的理想选择。

设计HDB3编码器ASIC的过程通常包括以下几个步骤:首先,利用Verilog HDL(硬件描述语言)进行前端设计,然后在工具如Quartus II上进行编译和仿真。接下来是综合、门级仿真和硬件验证,以确保设计的正确性和可靠性。最后,进行后端的版图设计,这涉及到物理布局和布线,以适应实际的制造工艺和性能要求。

在HDB3编码器的硬件描述语言设计中,编码的逻辑主要基于AMI码的转换规则,即将输入的“1”交替转换为+1和-1,同时监控并处理连续的“0”序列。如果出现四个或更多连续的“0”,则会根据编码规则插入“V”码,以保持码流的交替特性。这种设计思路确保了HDB3编码器能够有效地进行码型转换,从而实现高效、无误的数字通信。

186 浏览量

155 浏览量

155 浏览量

2022-09-14 上传

128 浏览量

205 浏览量

点击了解资源详情

227 浏览量

weixin_38703955

- 粉丝: 2

最新资源

- 掌握PerfView:高效配置.NET程序性能数据

- SQL2000与Delphi结合的超市管理系统设计

- 冲压模具设计的高效拉伸计算器软件介绍

- jQuery文字图片滚动插件:单行多行及按钮控制

- 最新C++参考手册:包含C++11标准新增内容

- 实现Android嵌套倒计时及活动启动教程

- TMS320F2837xD DSP技术手册详解

- 嵌入式系统实验入门:掌握VxWorks及通信程序设计

- Magento支付宝接口使用教程

- GOIT MARKUP HW-06 项目文件综述

- 全面掌握JBossESB组件与配置教程

- 古风水墨风艾灸养生响应式网站模板

- 讯飞SDK中的音频增益调整方法与实践

- 银联加密解密工具集 - Des算法与Bitmap查看器

- 全面解读OA系统源码中的权限管理与人员管理技术

- PHP HTTP扩展1.7.0版本发布,支持PHP5.3环境