VHDL设计:HDB3编码器在数据传输系统中的应用

176 浏览量

更新于2024-08-28

1

收藏 265KB PDF 举报

"基于EDA的数据传输系统的HDB3编码器设计与实现,使用VHDL语言进行编码器的VHDL建模。"

在数字通信系统中,基带信号的传输是一个关键环节,尤其在无需载波调制解调的场景下。本资源主要讨论了一种用于数据传输系统的HDB3编码器的设计方法。HDB3码,全称为三阶高密度双极性码,是对AMI码的一种优化,旨在解决AMI码中可能出现的四连零序列问题,以利于接收端的定时恢复。由于HDB3码具有无直流分量、低频成分少以及连续零个数最多不超过三个的特性,它被国际电信联盟(CCITT)推荐作为基带传输的标准码型。

HDB3编码规则的核心是确保连0串不超过三个。如果原始二进制消息代码中存在四连零或更长的连0串,编码规则会插入一个与前一个非零符号同极性的V符号(+V或-V),并保持V符号之间极性的交替。此外,如果相邻V符号之间的非零符号数量为偶数,会在当前V符号之前的第一个0位置插入B符号,B符号的极性与前一个非零符号相反,从而确保非零符号序列从V符号开始继续交替。

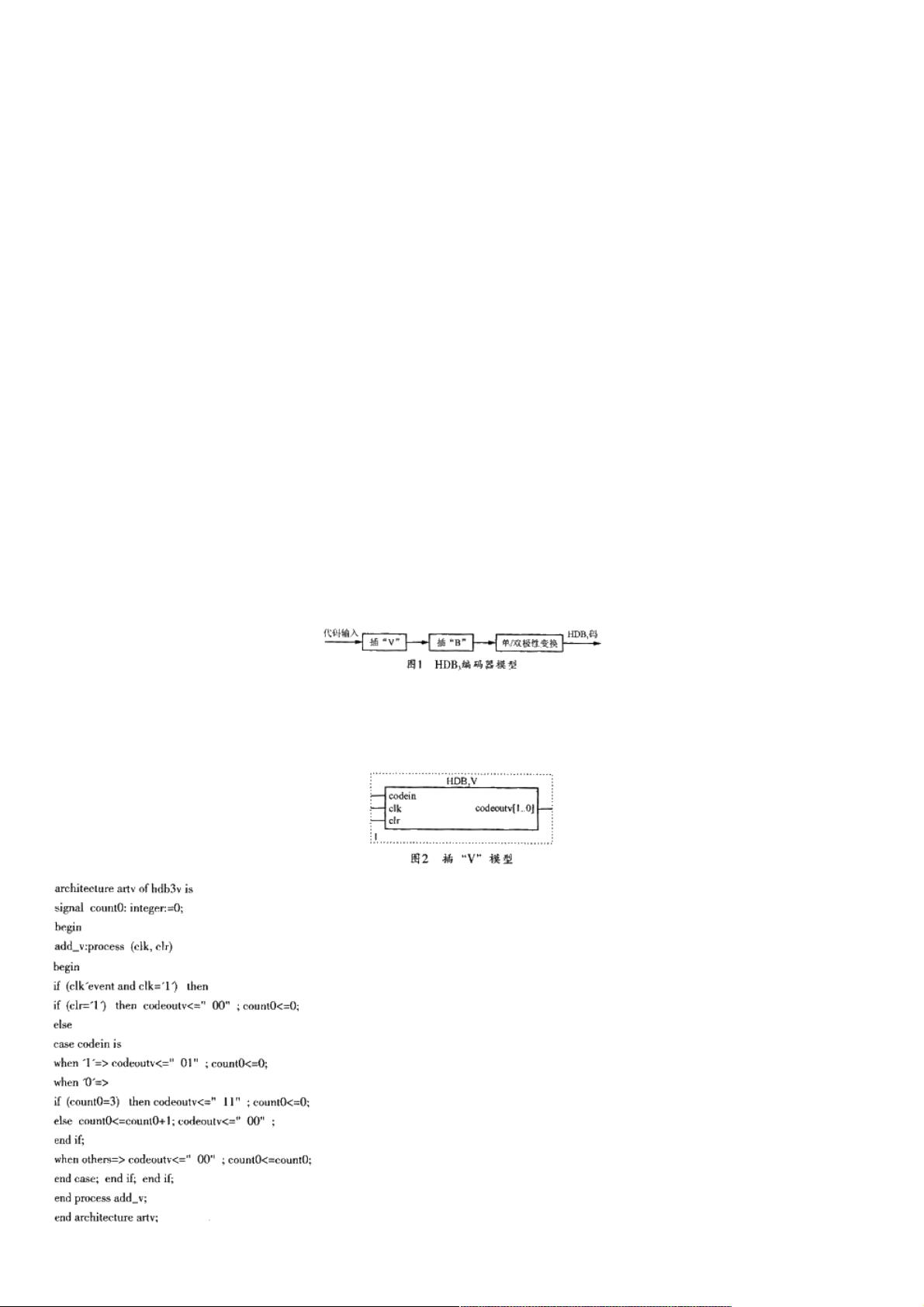

在实现HDB3编码器时,通常采用硬件描述语言VHDL进行建模。VHDL是一种用于电子设计自动化(EDA)的编程语言,允许设计者精确地描述数字系统的逻辑功能。在VHDL中,编码器的模型会包括检测和处理连0串的模块,例如插入V符号的模块,以及根据需要插入B符号的模块。这些模块会根据HDB3编码规则动态地修改输入的二进制数据流,以生成符合HDB3码的双极性输出。

VHDL建模通常涉及实体、结构体、进程等概念,其中实体定义接口,结构体描述逻辑实现,进程则用于描述系统的时序行为。具体到HDB3编码器,可能包含一个主进程来跟踪输入序列,以及多个子进程来处理特定编码规则,如检测四连零、插入V和B符号等。通过这种方式,设计者可以构建出一个完整的HDB3编码逻辑电路模型,然后在仿真工具中验证其正确性,最后可能在FPGA或ASIC上实现硬件原型。

HDB3编码器的设计与实现是一项结合了数字通信理论和VHDL编程技术的工作,对于理解数字通信系统中码型变换的重要性以及如何用现代EDA工具实现这样的功能具有实际价值。通过这样的设计,可以有效地提升数字通信系统的性能和可靠性。

2009-12-23 上传

2023-06-20 上传

2020-10-18 上传

2020-12-03 上传

2020-12-04 上传

2020-11-12 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38633157

- 粉丝: 5

- 资源: 968

最新资源

- MyProjects:Meus projetos

- strip-ansi-escapes

- aws-cicd-workshop-cpt

- OPPOA71 73 79 手机 原厂维修图纸电路图PCB位件图资料.zip

- elasticsearch:此仓库用于在ppc64le的ubi8上创建用于Elasticsearch的映像

- portfolio-project

- HitboxPlugin:BakkesMod Hitbox 插件

- Android ActionSheet动画效果实现

- google-homepage

- LoadingImageView:UIImageView 的加载指示器,用 Swift 编写

- SCHOOL-WEBSITE

- aayushmau5

- 参考资料-72_企业职工离职管理制度.zip

- arrayhua.github.io:高级开发工程师简历

- 类似UC 浏览器复制功能

- groot:使用子模块管理 git 存储库(已失效)