RV32M标准下的乘除法运算器实现探讨

需积分: 0 10 浏览量

更新于2024-08-05

收藏 7.1MB PDF 举报

"基于RV32M标准的运算器实现(论文)1"

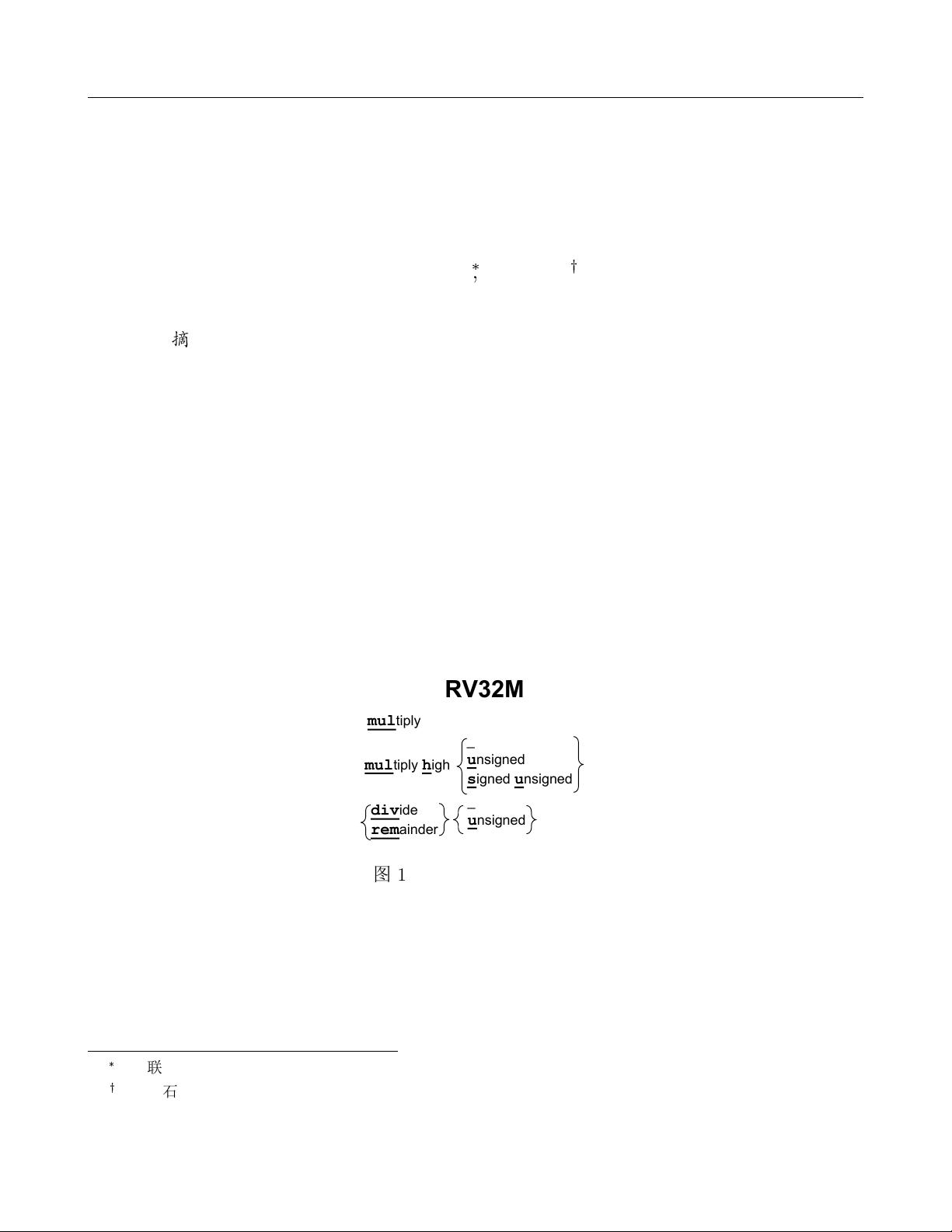

本文主要探讨了在基于RV32M标准的运算器实现中,如何利用特定算法来设计和实现乘法器与除法器。RV32M是RISC-V(Reduced Instruction Set Computer - V)架构的一个扩展,专门针对整数乘法和除法运算,提供了八种相应的指令。这些指令允许对有符号和无符号整数进行乘法,并对相同数集的整数执行除法。乘法运算可能涉及有符号乘以无符号的操作数,而除法则相对简单,操作数都属于同一数集。

乘法器和除法器的实现通常需要考虑如何高效地处理补码表示的负数。基本的移位累加和试减法虽然适用于正数运算,但在处理补码表示的负数时会变得复杂。因此,文章提到了两种常用的算法,即Booth算法和不恢复余数算法,以适应补码运算的需要。Booth算法通过减少乘法中的位移次数来提高效率,而不恢复余数算法则在除法过程中避免了对余数的恢复步骤,简化了计算流程。

在介绍这两种算法之前,作者首先阐述了RISC-V架构的基本原理,即其精简指令集的特点,以及为什么需要扩展到包含乘法和除法指令。RISC-V的开放源代码特性使得该架构在全球范围内得到了广泛应用,因此,对于这个扩展标准的研究和实现具有重要的实际意义。

在RV32M中,乘法指令产生的结果通常是高位和低位的积,而除法指令则产生商和余数。理解这一点对于设计硬件乘法器和除法器至关重要,因为它们需要能够分别处理这些结果的不同部分。在硬件实现上,乘法器通常采用组合逻辑电路,如阵列乘法器,而除法器可能需要更复杂的顺序逻辑,如迭代或分步过程。

文章引用了William of Occam的"奥卡姆剃刀"原则,强调在设计中应尽可能保持简洁。这在设计高效的乘法器和除法器时尤其重要,因为复杂的实现可能会增加硬件成本和功耗。

这篇论文深入探讨了在RISC-V RV32M扩展下实现乘法器和除法器的算法选择和设计考虑,为硬件开发者提供了实用的理论基础和技术指导。通过理解并应用文中提到的Booth算法和不恢复余数算法,可以设计出更加高效、适应性强的运算器,以满足现代计算机系统对快速和精确算术运算的需求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-02-09 上传

2024-11-28 上传

2024-09-29 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

VashtaNerada

- 粉丝: 28

- 资源: 297

最新资源

- Chausie提供了可自定义的视图容器,用于管理内容页面之间的导航。 :猫:-Swift开发

- DianMing.rar_android开发_Java_

- Mockito-with-Junit:与Junit嘲笑

- recycler:[只读] TYPO3核心扩展“回收者”的子树拆分

- 分析:是交互式连续Python探查器

- emeth-it.github.io:我们的网站

- talaria:TalariaDB是适用于Presto的分布式,高可用性和低延迟时间序列数据库

- lexi-compiler.io:一种多语言,多目标的模块化研究编译器,旨在通过一流的插件支持轻松进行修改

- 实时WebSocket服务器-Swift开发

- EMIStream_Sales_demo.zip_技术管理_Others_

- weiboSpider:新浪微博爬虫,用python爬取新浪微博数据

- Vue-NeteaseCloud-WebMusicApp:Vue高仿网易云音乐,基本实现网易云所有音乐,MV相关功能,转变更新到第二版,仅用于学习,下面有详细教程

- asciimatics:一个跨平台的程序包,可进行类似curses的操作,外加更高级别的API和小部件,可创建文本UI和ASCII艺术动画

- Project_4_Java_1

- csv合并js

- containerd-zfs-snapshotter:使用本机ZFS绑定的ZFS容器快照程序