VHDL入门教程:行为描述与数据流风格解析

需积分: 7 199 浏览量

更新于2024-07-29

收藏 243KB PDF 举报

"VHDL入门2-2.pdf - 学习VHDL硬件设计语言的基础知识,包括行为描述和数据流描述两种架构风格"

在电子设计自动化领域,VHDL(VHSIC Hardware Description Language)是一种广泛使用的硬件描述语言,用于设计和验证数字系统,如FPGA和ASIC。本资料提供了VHDL的入门教程,主要讲解了两种主要的VHDL架构描述风格:行为风格(Behavioral Style Architecture)和数据流风格(Dataflow Style Architecture)。

1. 行为风格架构(Behavioral Style Architecture)

行为风格的描述主要关注输入到输出的逻辑转换,而不涉及具体的硬件实现细节。它允许设计者使用函数、过程和进程语句来描述系统的逻辑行为。在给出的例子中,`PROCESS(a,b)`是一个进程,它对输入`a`和`b`进行比较,并根据比较结果更新输出`equals`。当进程中的敏感列表中的信号(如`a`或`b`)发生变化时,进程会被触发执行。这种风格强调的是系统行为的顺序描述,例如使用`IF`语句来表达条件判断。

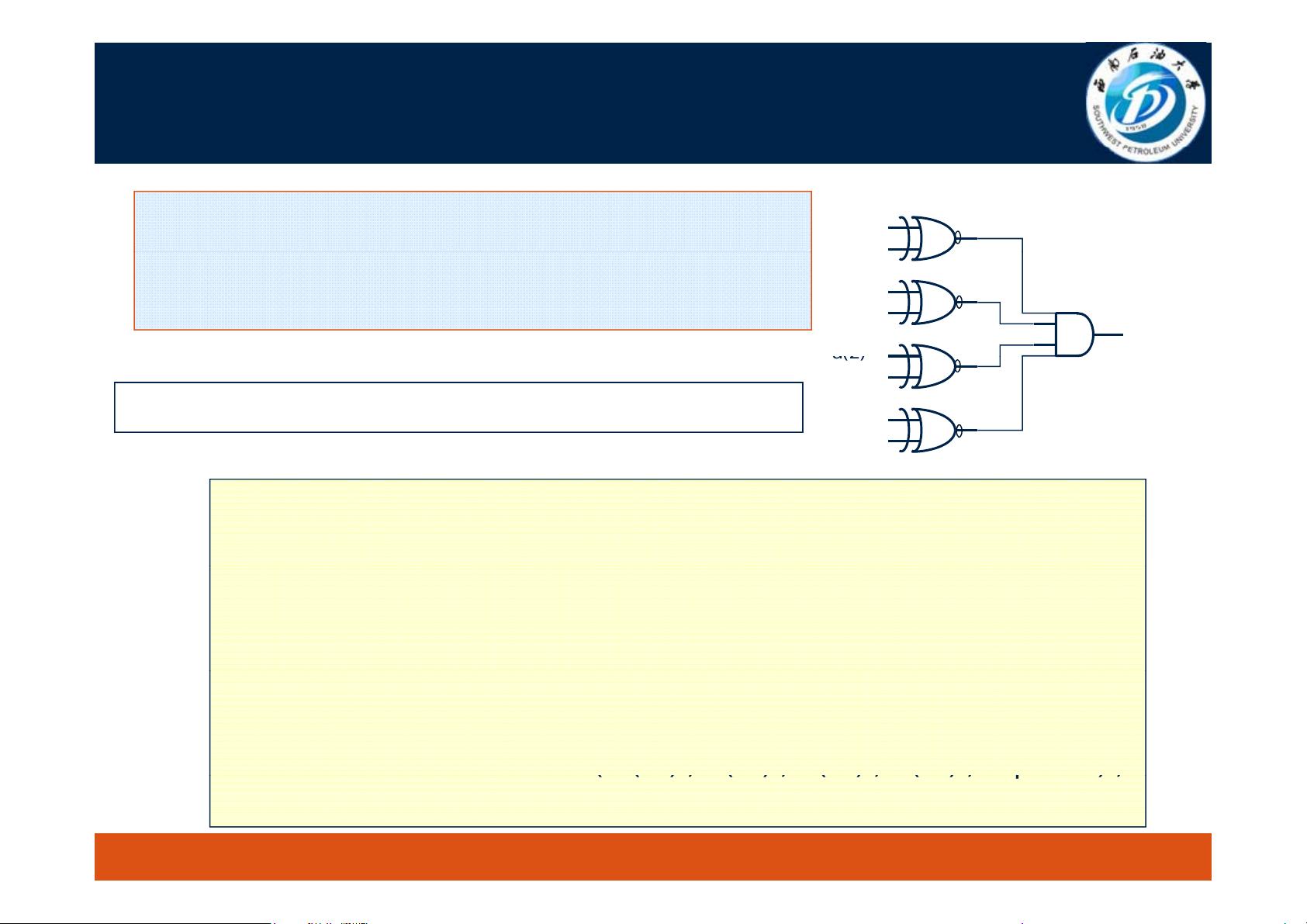

2. 数据流风格架构(Dataflow Style Architecture)

数据流风格的描述更接近于寄存器传输级(Register Transfer Level, RTL)的设计,它强调信号之间如何通过并行的信号赋值语句进行数据传递,而不使用顺序语句。在给出的示例中,`equals`的值直接由`a`和`b`的逐位异或操作结果进行逻辑与运算得到,这显示了数据如何从输入信号流经设计单元到达输出,同时隐含了其内部的结构。

这两种描述风格各有优势:

- 行为风格更适合于描述复杂的算法和控制逻辑,它提供了高级别的抽象,使得设计的逻辑更容易理解。

- 数据流风格则更适合于描述并行处理和简单的组合逻辑,因为它直接展示了信号之间的数据流动路径。

在实际设计中,通常会结合使用这两种风格,以达到最佳的抽象层次和实现效率。了解和掌握VHDL的这两种描述方式是成为合格的数字系统设计师的基础,也是进行FPGA和ASIC设计的关键技能。

2020-04-30 上传

215 浏览量

2022-09-23 上传

2021-08-11 上传

2022-09-19 上传

2023-04-23 上传

binshao199023

- 粉丝: 0

- 资源: 4

最新资源

- ssmcache:这是一个简单的缓存库,仅从SSM参数存储中检索参数

- spot-playground:试用Spot和OpenAPI客户端生成器

- ZoomInfo ReachOut: B2B Contact & Company Info-crx插件

- VB仿LED中英文滚动字幕显示屏

- latex_3d_objects_with_sketch:在Tex中使用草图绘制3D对象

- WN86.github.io:Hexo博客

- DS1302.zip_VHDL/FPGA/Verilog_VHDL_

- React-Expense-Tracker

- ml:机器学习测试库

- naughty-bobby:一个名为Bobby的顽皮孩子在打向北极的途中大声疾呼圣诞老人的屁股的游戏

- 欧姆龙(OMRON)CP1E经济型PLC中文样本

- PyPI 官网下载 | smartnoise-synth-0.2.1.tar.gz

- faux:有用的软件包的集合

- matlab心线代码-eNRBM:EMR驱动的非负受限玻尔兹曼机

- has-reflect-support-x:测试是否支持ES6 Reflect

- dbaddinslides:DB Addin的幻灯片