数字逻辑实验:触发器功能测试与比较

需积分: 14 30 浏览量

更新于2024-08-04

1

收藏 327KB DOCX 举报

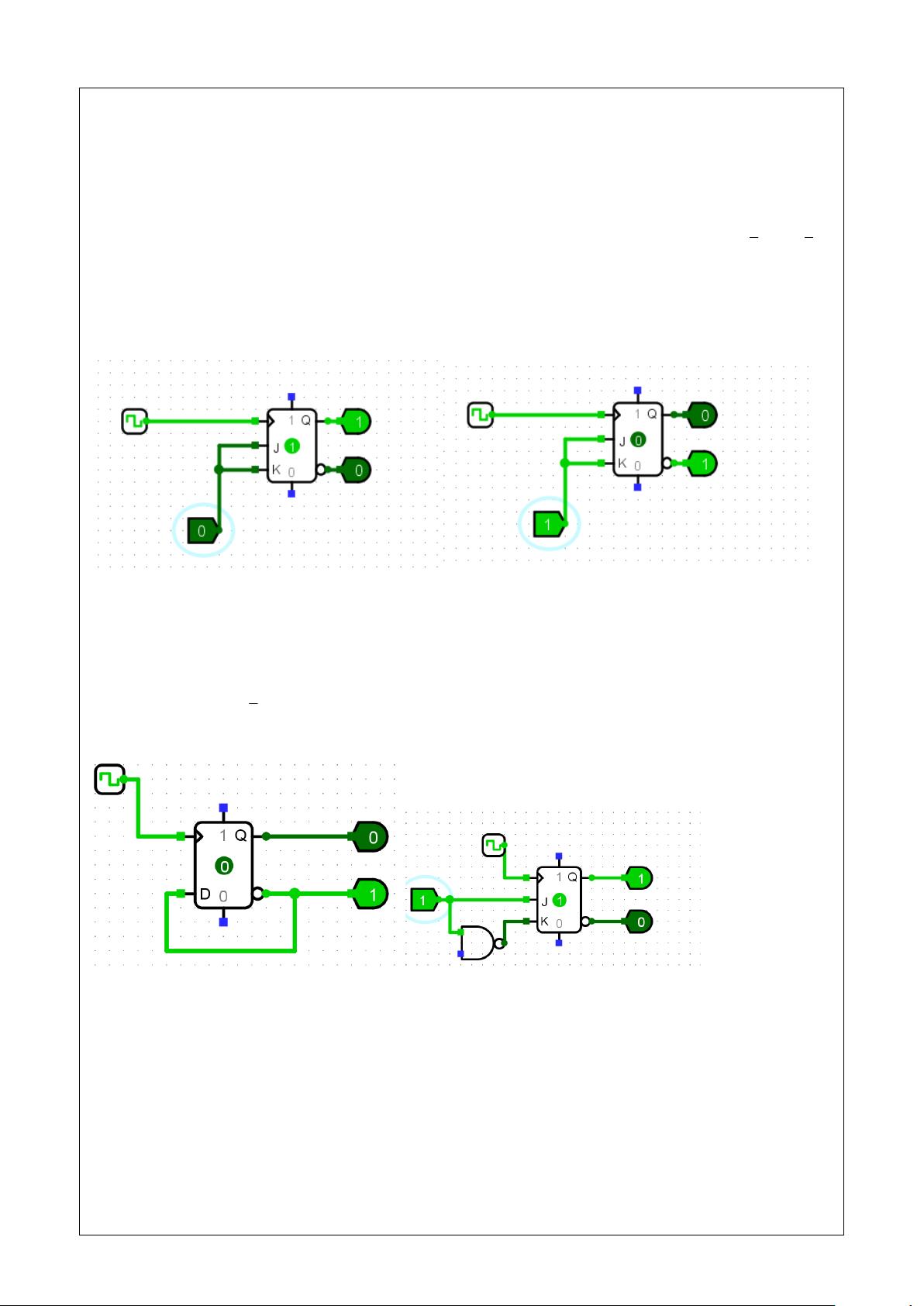

"该实验报告主要探讨了触发器的应用,特别是对时钟控制的RS触发器、JK触发器,以及主从结构的RS触发器和JK触发器的比较。实验内容包括测试不同类型的触发器(JK、D、T)的逻辑功能,理解触发器之间的逻辑转换,以及它们在实际应用中的基本原理。此外,实验还涵盖了单次脉冲发生器和分频电路的构建,并对时钟控制与主从结构的触发器进行了深入分析。"

触发器是数字逻辑电路中的基础组件,用于存储和传输二进制状态。在本实验中,重点研究了以下几种触发器:

1. **RS触发器**:RS触发器是最基本的双稳态电路,由两个非门交叉连接形成。时钟控制的RS触发器通过时钟信号来决定输入信号何时生效,以避免不确定状态。而在主从结构中,数据的设置和清除发生在时钟边沿,确保了数据传输的稳定。

2. **JK触发器**:JK触发器是RS触发器的一种改进形式,提供了更为灵活的翻转控制。J和K输入分别代表“设置”和“清除”,但当两者同时为1时,触发器会翻转其状态,或者保持当前状态(如果存在反馈回路)。

3. **D触发器**:D触发器以数据(D)输入命名,它在时钟上升沿或下降沿捕获D输入的状态,使得输出Q在时钟边沿后与D相同。D触发器常用于数据锁存和定时电路。

4. **T触发器**:T触发器根据T输入的值来翻转或保持输出状态。当T为1时,输出会在时钟边沿翻转;若T为0,则输出保持不变。

实验目的不仅在于理解这些触发器的逻辑功能,还包括学习如何在实际应用中进行触发器间的逻辑转换。例如,通过适当门电路的组合,可以将JK触发器转换为D触发器或T触发器。此外,单次脉冲发生器和分频电路的构建展示了触发器在脉冲处理和频率控制中的应用。

单次脉冲发生器利用触发器的翻转特性,仅在接收到一次输入脉冲时产生一个输出脉冲。而分频电路则是通过触发器和逻辑门的组合,将输入时钟的频率除以特定数值,产生较低频率的时钟信号。

对于时钟控制RS触发器和主从钟控RS触发器、JK触发器的比较,主要关注的是它们的边沿触发和电平触发的区别,以及主从结构带来的抗干扰能力和同步性能的提升。主从结构的触发器在时钟边沿前后有明显的区分,确保了数据在时钟边沿瞬间的准确捕捉,提高了系统的稳定性。

通过这个实验,学生可以深入理解触发器的工作原理,熟悉其在数字逻辑系统中的作用,为后续的数字电路设计和分析奠定坚实的基础。

2021-10-22 上传

2020-07-15 上传

2023-12-18 上传

2021-10-06 上传

2022-11-23 上传

2021-10-12 上传

2022-07-13 上传

2022-06-25 上传

2021-10-07 上传

lfn.

- 粉丝: 3

- 资源: 15

最新资源

- ArtLinks:链接到我所有的艺术作品

- exam-countdown:一个帮助我跟踪即将到来的考试的小网站

- Excel模板客户登记表.zip

- PV8_PEMFC8_battery10_inverter_ACload_LC_grid_储能_SIMULINK_Battery

- PrivacyBreacher:旨在展示Android操作系统中的隐私问题的应用

- 毕业设计&课设--东南大学本科毕业设计(论文)模版.zip

- magnitude-to-number:将十亿,百万和万亿字符串转换为整数

- txt_wysiwyg:互联网的 TXT WYSIWG 编辑器

- my-delivery-boy

- 485_UART2实验_485采集温湿度_STM32F103_STM32uart2_modbus解析_rs485

- 核

- Yakov_Fain-Book:雅各布精美书

- pi4-cluster-ansible-roles:Ansible角色,用于执行Raspberry Pi 4工作程序节点的初始设置(尚无k8s软件)

- OfficeManagementSystem:一种有助于执行办公室日常活动的系统,包括出勤管理,任务管理,休假管理,投诉管理等

- 毕业设计&课设--高校校园设备管理系统-毕业设计.zip

- FitnessTracker:使用Spring Boot的Fitness Tracker RESTful Web应用程序