VHDL频率计程序设计详解与Quartus实现

需积分: 16 16 浏览量

更新于2024-09-08

收藏 147KB DOC 举报

本文档详细介绍了如何使用VHDL语言设计并实现一个8.16位数字频率计程序。该程序的主要目标是实时测量并显示输入信号的频率,采用四位数码管动态显示结果,并以千赫兹(KHz)为单位。设计的核心部分包括一个四位十进制计数器(b1至b4)和一个BCD码转换器,用于将计数结果转换成可显示的编码。

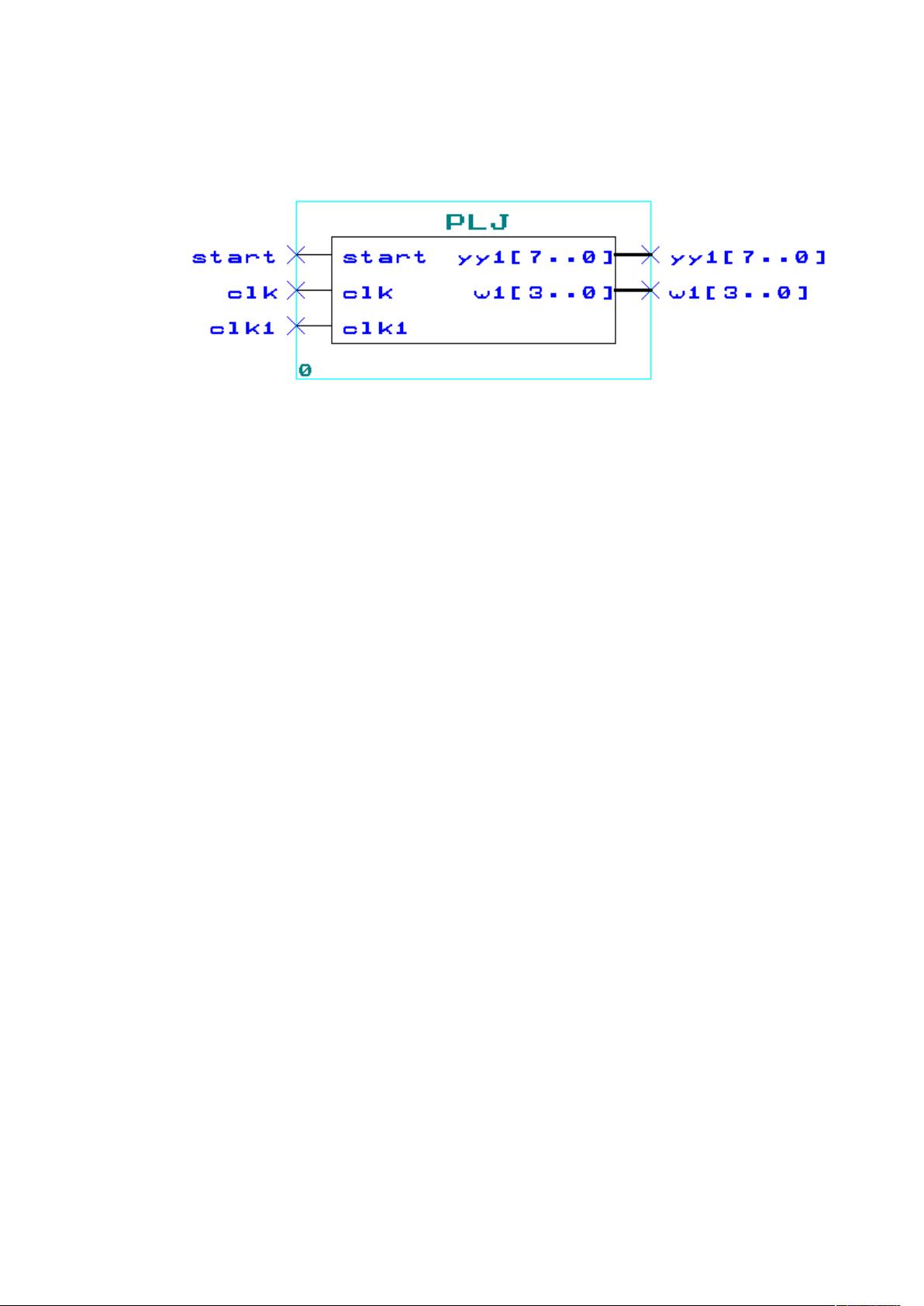

在程序结构中,首先定义了实体(plj),包含了输入端口如复位信号(start)、系统时钟(clk)和被测信号(clk1),以及输出端口如八段码(yy1)和数码管位选信号(w1)。接着,展示了实体的架构部分,定义了多个信号变量,如十进制计数器(b1~b7)、BCD码寄存器(bcd)、秒分频系数(q)和动态扫描分频系数(qq),以及一些控制信号如使能信号(en)和小数点sss。

两个主要的进程被设计来处理频率计数和控制流程。第一个进程(second)基于系统时钟(clk)进行工作,当复位信号为1时,清零计数器q,然后在时钟上升沿触发时,q递增,直到达到最大值后重新置零。当计数器处于非满状态且复位信号为0时,使能信号en被激活,以便于后续处理。第二个进程(and2)则依赖于使能信号en和被测信号clk1,当两者都有效时,它负责处理计数器的更新和BCD码的转换,以保证频率计的实时性和准确性。

bcd0~bcd3变量用于存储计数器中有效高四位的数据,这有助于确保小数点位置的正确性。BCD码转换的目的是为了适应数码管的显示需求,因为通常数码管直接驱动的是BCD码形式的信号。

整个程序还包含详细的注释,使得初学者可以更好地理解和仿真实现。通过在Quartus等工具上编译和运行此VHDL代码,用户可以验证程序的功能并在实际硬件中看到频率计的实时工作情况。这份文档提供了一个实用的频率计程序设计实例,对于学习VHDL编程和理解数字电路设计非常有价值。

274 浏览量

2021-10-11 上传

115 浏览量

112 浏览量