FPGA设计全流程详解:Modelsim、Synplify及ISE关键步骤

需积分: 12 181 浏览量

更新于2024-09-09

收藏 236KB PDF 举报

FPGA设计是一个复杂而细致的过程,它涉及多个阶段和工具的协同工作。本文将详细介绍FPGA设计的全流程,从Modelsim的库编译开始,直到使用Xilinx CORE Generator生成可重用的IP内核。

1. Modelsim编译Xilinx库

Modelsim是常用的FPGA验证工具,首先需要对Xilinx提供的核心库进行编译。这包括sim_prims、unisims和XilinxCoreLib这三个库。用户需在Modelsim的安装目录下创建一个名为XilinxLib的文件夹,并将其设置为工作目录。接着,用户会在这个目录中编译这三个库,通过“Compile”菜单选择相关文件并进行编译。

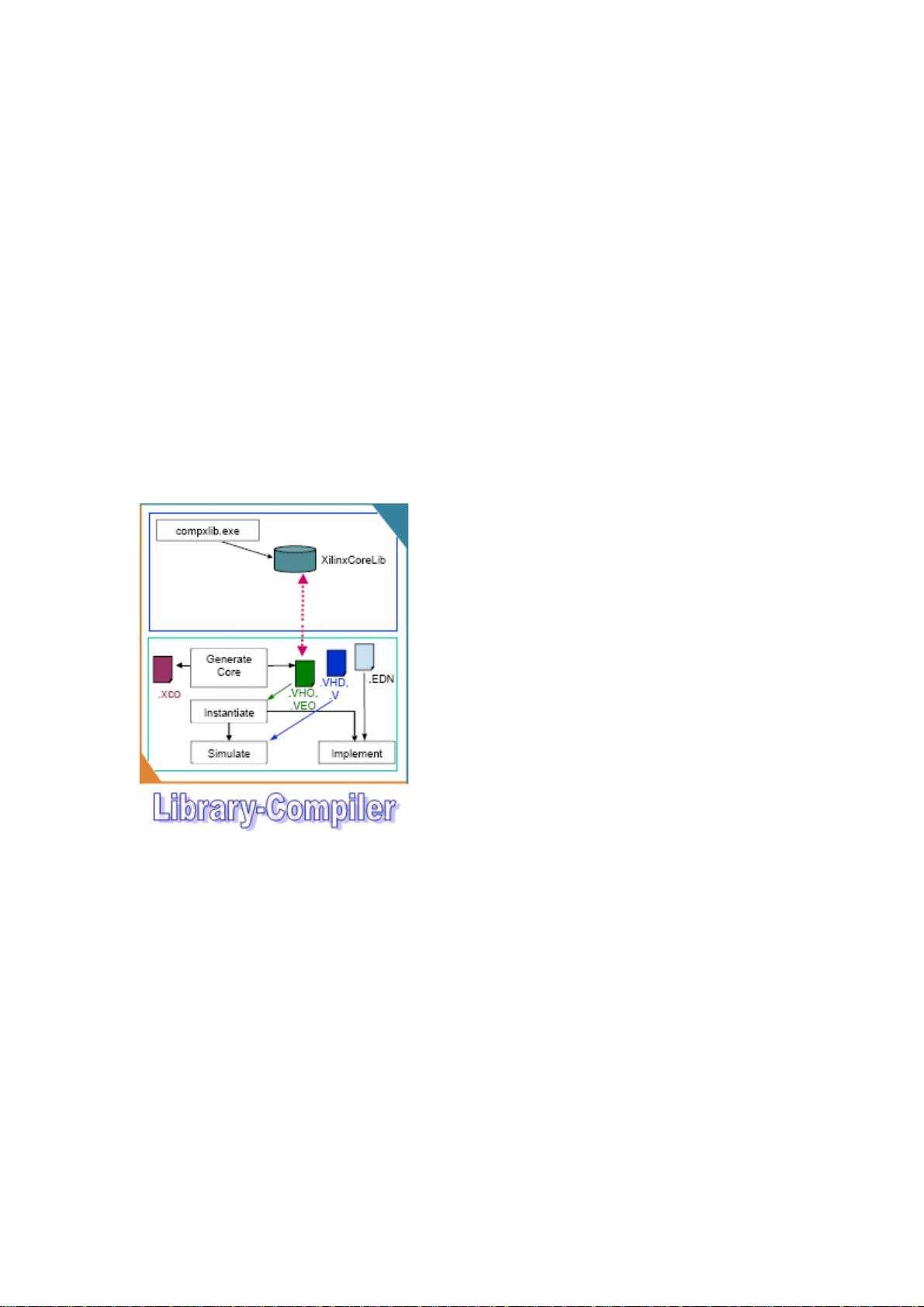

2. Xilinx CORE Generator应用

CORE Generator是FPGA设计的关键环节,它允许设计师创建可配置的IP模块,即自定义硬件组件。这些IP可以是参数化的,以便适应不同的设计需求。用户可以通过CORE Generator来设计并生成这些IP,无论是基于原理图还是HDL(如VHDL或Verilog)。

3. HDL集成与综合

在设计过程中,通常使用如Synplify.Pro这样的高级综合工具,将HDL代码转换成FPGA可识别的逻辑。设计师需要将HDL代码和预先编译好的内核结合,然后通过Synplify.Pro进行综合,生成网表文件,这是实际实施设计的基础。

4. 项目执行与仿真

综合后的项目,模型需要在Modelsim等仿真器中进行验证。这包括不同类型的结构仿真,如功能仿真、时序仿真等,确保设计的正确性和性能。在Modelsim中,除了库的编译,还包括设计本身的仿真,以便发现和修复潜在问题。

5. IP核的生成与应用

在完成设计和验证后,生成的IP核可以被整合到更大的FPGA设计中。通过CORE Generator,IP核可以作为一个黑箱模块,实现复用和灵活性,显著减少设计时间和复杂性。

总结起来,FPGA设计全流程涉及库管理、HDL编程、IP核生成与集成、以及详细的验证过程。每个步骤都需要熟练掌握相应的工具和技术,以确保最终设计的高质量和效率。通过遵循这个流程,设计师能够构建出功能强大且可扩展的FPGA解决方案。

2011-04-09 上传

2022-09-23 上传

2009-03-17 上传

379 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

152 浏览量

535 浏览量

tuma

- 粉丝: 0

- 资源: 1