静态时序分析:门延时计算的精确模型与Π方法优化

200 浏览量

更新于2024-08-30

收藏 178KB PDF 举报

静态时序分析是一种关键的集成电路设计验证技术,在微系统芯片(SoC)设计中尤为重要。传统的逻辑模拟方法在SoC时代面临着挑战,主要表现在速度慢、精度低,无法有效处理复杂的互连线效应。电路模拟虽然精确但速度慢且容量有限。静态时序分析则通过提取所有时序路径,计算信号的上升沿或下降沿延时,检查建立时间和保持时间是否满足要求,以确定电路是否存在时序问题。

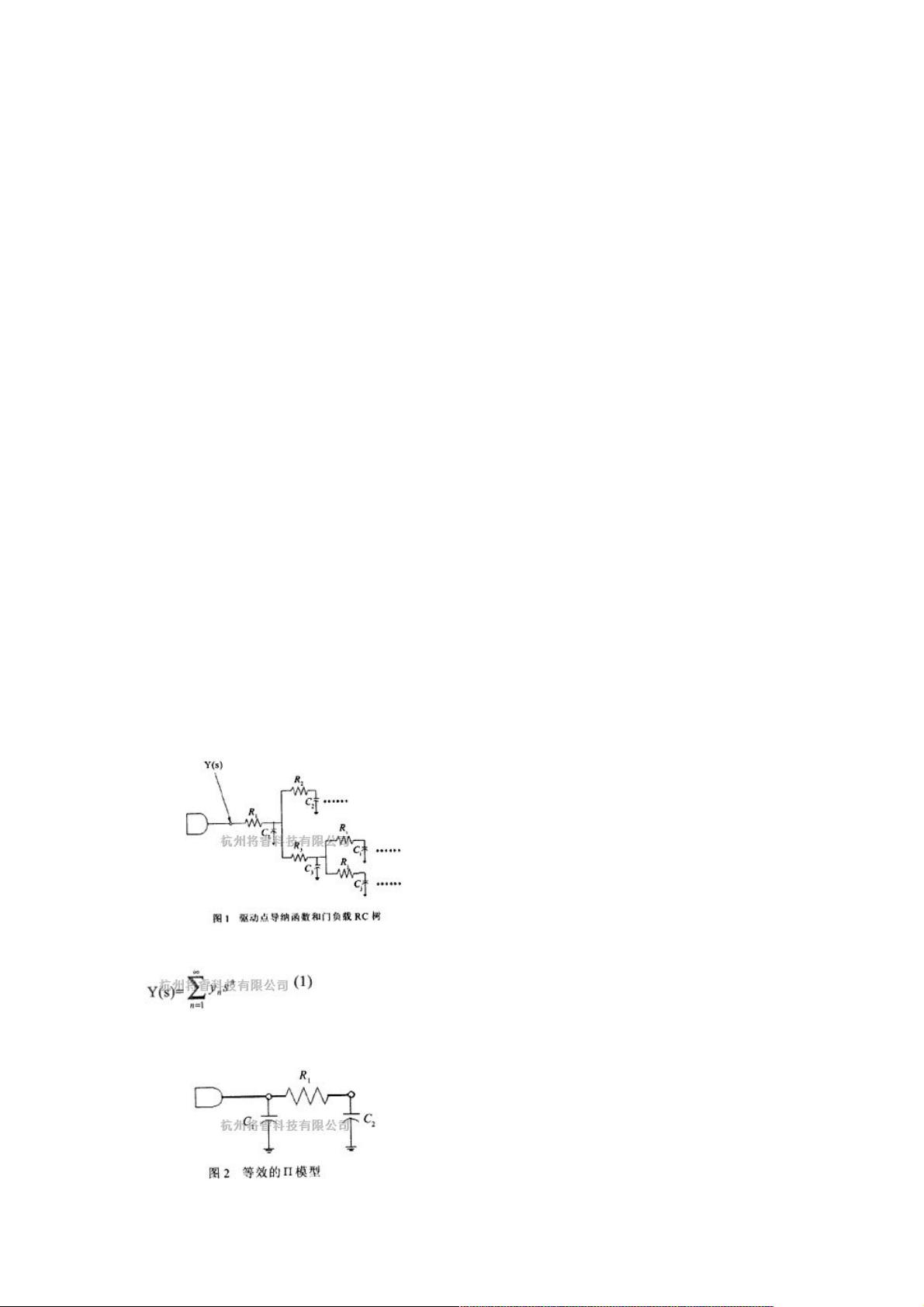

静态时序分析的核心在于最大路径延迟和最小路径延迟的分析,这与门延时计算密切相关。互连线结构对门延时的影响巨大,因此在门延时模型中必须考虑到这种影响以保证分析结果的准确性。现有的门延时模型,如Π型的RC模型,可以近似门的互连线输出负载并考虑屏蔽效应,通过计算导纳函数的前几阶系数来估算门延时。

本文介绍了一种新的门延时计算方法,即结合门的等效电容和互连线负载的拓扑结构,利用门负载的三阶矩求解公式,进一步优化了延时计算模型。这种方法相较于传统的模型更加合理,能够更准确地反映门延时的实际影响,从而提升静态时序分析的精度和效率。这种改进对于现代集成电路设计而言,尤其是在SoC设计中,具有显著的实际意义,有助于提高设计质量和降低设计周期。通过优化的门延时模型,设计者可以在保证时序正确性的前提下,更好地应对复杂的设计挑战。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-10-10 上传

2019-02-27 上传

2012-11-17 上传

2018-03-26 上传

2010-06-05 上传

2020-08-04 上传

weixin_38677725

- 粉丝: 5

- 资源: 932

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率