Advuttd

DigitaJ D esign with

the

Verilog

HDL

HDLs

and

synlhesis lools focus

an

engin

ee

r's allention on functionality rather

than

on

individual transistors or gates; they synthesize a

ci

rcuit that will r

ea

li

ze the de-

sired functionalit

y,

and

satisfy a rea

andlor

performance constraints. Moreover, alterna-

tive architectures can

be

generated

fr

om a single

HDL

model and evaluated quickly to

perform design tra

de

offs. Functional models

ar

e also referred to as behavioral model

s.

HDLs

serve as a platform for

seve

ral

too

l

s:

design e ntry, design ver

ifi

cation. test

generation, fault analysis

and

simulation,

ti

ming analysis and/or

ve

rification, synthesi

s,

and

automatic generation

of

sc

hematics. This

br

eadth

of

use improves the efficiency of

the design now by eliminating translations

of

de

sign descriptions as t

he

design moves

through the tool chain.

Tw

o languages enjoy wides

pr

ead industry s

up

port:Veril

og

U I

(lJ

and

VHDL

[2

J.

Both languages are I

EEE

(In

stitute

of

Electrical

and

Electronics Engincers) stan-

dards;

both

are supported by synthesis tools for ASICs

(app

li

cation-speci

fic

integrated

circuits) a

nd

FPGAs

(field-pr

og

rammabl

e

gale

arrays). Languages

fo

r

ana

log

ci

rcuit

dc

sign, such as Spice (3). play an impo

rt

ant role in verifying critical timing paths

of

a

ci

rcuit,

but

these languages impose a prohibitive co

mput

ational

burd

en

on

large de-

si

gn

s,

cannot support abstract styles

of

design,

and

become impractical when used on a

large scal

c.

Hybrid languages (e.g

..

Verilog-

A)

(4)

are used

in

designing mixed-signal

circuits, which have both di

gi

tal and analog circuitry. System-level design languages,

such as SystemC

[5J

and SuperlogTM 16], are now emerging to support a higher level

of

de

sign abstrac

ti

on than

ca

n

be

s

up

po

rted by Veril

og

or

VHDL.

1

.1

Design Methodology-An Introduction

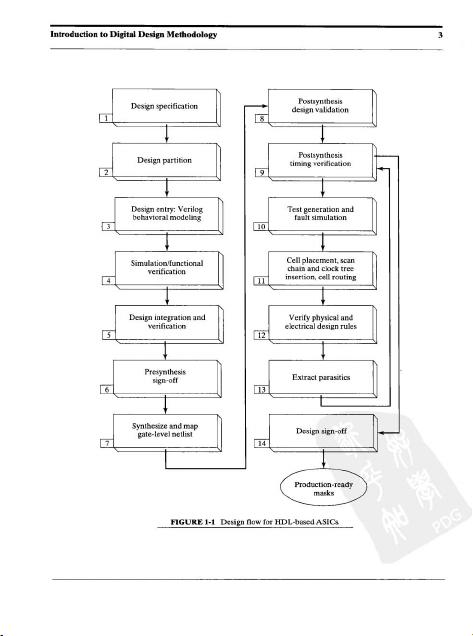

ASICs

and

FPG

As are design

ed

systematically to maximize

the

likelih

ood

that a de-

sign will

be

correct and will be fabricated

wi

thout fatal naw

s.

Designers follow a "de-

sign now" like that shown in Figure 1-1, which specifies a se

qu

ence of maj

or

steps

that

will be taken to design.

ve

rif

y,

synth

es

ize.

and

test a digital circuit.

ASIC

design nows

in

vo

lve several activitie

s,

from specificati

on

and

design entry.

to

place-

and

-route and

timing closure

of

the circuit in s

il

icon. Tuning

cl

osure is attain

ed

when all of the signal

paths in the design satisfy the timing constraints imposed by the interface circuitry, the

circuit's sequential elements,

and

the system

cl

ock. Although the desi

gn

fl

ow

appears

10

be

linear, in practice

it

is not. Various steps might

be

revisited as design errors are

discovered, requir

eme

nts change,

or

per

f

orma

nce a

nd

design constraints are violatcd.

For example, if a circuit

fa

il

s to m

eet

timing constraints, a new place

ment

and

routing

step

will have to be taken,

perhaps

including redesign

of

critical paths.

Design nows f

or

standard-cell-based ASJCs

ar

e

more

complcx than those

fo

r

FP

GAs because the architecture of

an

ASIC is not

fix

e

d.

Consequcntly, the perfor-

mance that can

be

realized from a d

es

ign de

pend

s

on

the physical placement

and

r

ou

t-

ing

of

the cells on the die, as we

ll

as

the underlying device properties. Inte rconnect

delays play a significant role in delcrmining performance in submicron designs below

0.18

pm

, in which p

re

layout

estimates

of

path

delays do

not

gu

arantee

timing clos

ure

of

the routed design.

Th

e following sections will clarify the design flow described in Fig

ure

1-1.