Verilog实现16位环形移位寄存器及其原理分析

需积分: 17 19 浏览量

更新于2024-08-07

1

收藏 845KB PDF 举报

该资源是关于“实验三 16位环形移位寄存器”的讲义,主要内容涉及D触发器的原理、Verilog HDL设计,移位寄存器的设计,以及按钮开关消抖电路,并介绍了实验所需的设备和软件。

在数字逻辑电路中,16位环形移位寄存器是一个重要的时序逻辑组件,主要用于存储和处理数据。这个实验主要分为以下几个部分:

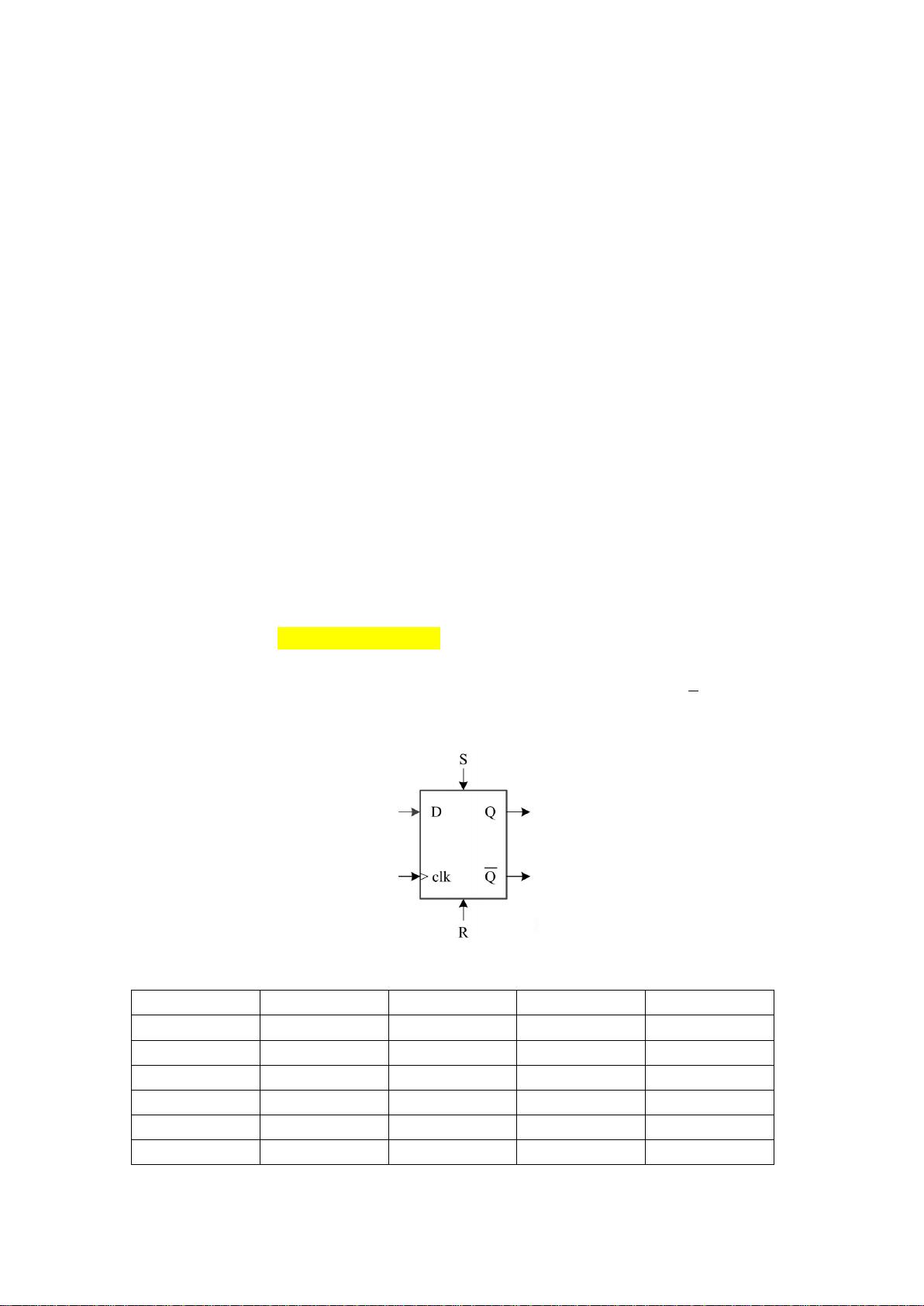

1. D触发器:D触发器是基本的存储单元,它在时钟的上升沿或下降沿对输入D的值进行采样并保存在输出Q上。在Verilog HDL中,D触发器可以被描述为一个模块,其中包含时钟(clk)、清零(clr)、置位(set)和数据输入(D)信号,以及输出Q。D触发器的状态方程简单明了,即Qn+1=D,表示在下一个时钟周期,输出Q的值将等于当前D的值。在Verilog代码中,使用`always @(posedge clk or posedge clr or posedge set)`来定义时钟边沿敏感的逻辑,并用非阻塞赋值操作符“<=”更新Q的值,以确保在时钟边沿之后进行赋值。

2. 移位寄存器:移位寄存器是多个D触发器的组合,用于存储一组数据并根据控制信号进行左移或右移操作。在16位环形移位寄存器中,数据可以在寄存器内循环移动,这在串行通信、数据处理和波形生成等领域有广泛应用。设计移位寄存器通常涉及到多个D触发器的级联,并添加适当的控制逻辑来实现移位操作。

3. 按钮开关消抖电路:在实际硬件系统中,物理按钮的按下和释放可能会导致多次电信号的波动,即抖动。为了获得稳定的输入,需要设计消抖电路。在Verilog中,可以通过滤波或者延时的方式来消除这种抖动,确保单次按键只产生一次有效的信号变化。

4. 时序逻辑电路设计方法:实验旨在让学生熟悉使用Verilog HDL设计时序逻辑电路的方法,包括理解时序逻辑的特点、时序逻辑电路的建模和仿真,以及如何在FPGA平台上实现这些设计。

实验所需设备包括Digilent公司的Basys3 FPGA开发板,配备Vivado 2017.4编程软件的电脑,以及USB连接线。通过这个实验,学生不仅能够学习到D触发器和移位寄存器的基本原理,还能掌握Verilog HDL的编程技巧,以及如何在实际硬件上验证和测试设计。

这个实验是一个全面的学习体验,涵盖了数字逻辑的基础知识和现代电子设计自动化工具的使用,对于提升学生的实践能力和理论理解都十分有益。

2020-07-18 上传

2022-07-14 上传

2021-10-04 上传

2021-11-01 上传

2022-11-13 上传

2021-07-13 上传

2021-07-13 上传

2019-10-12 上传

2023-05-28 上传

qq_58960835

- 粉丝: 0

- 资源: 4

最新资源

- 教你怎么写批处理.txt

- C语言 描述 数据采集 程序

- Oracle9i 数据库管理基础 I Ed 1.1 Vol.1

- intel平台的ELF 文件格式

- High.Performance.MySQL_Second.Edition.pdf

- 基于_NET企业信息资源管理系统的设计与实现

- Linux操作系统编程入门

- Ethereal用户手册.pdf

- 基于UDP通信协议的设计与实现

- 红外遥控系统原理及单片机软件解码实例

- 三言两语话Erlang

- java编程入门知识

- NET SQL Server数据访问抽象基础类

- linux 菜鸟过关

- Android 入门教程

- Oracle+9i&10g编程艺术:深入数据库体系结构