11.0592MHz UART波特率发生器:Verilog实现与串行通信详解

需积分: 33 63 浏览量

更新于2024-09-17

2

收藏 210KB DOC 举报

FPGA波特率发生器是一种在FPGA(Field-Programmable Gate Array)芯片上实现定制串行通信功能的关键组件,特别是用于调整串口RS232通信的波特率。RS232,全称是Recommended Standard for the Interface of Data Terminals Equipment,是一种广泛应用于电子设备之间串行通信的标准接口。

在设计FPGA波特率发生器时,关键的计算公式涉及到系统时钟频率(FSYS)和目标波特率(BaudRate)。例如,如果目标波特率为9600,且已知的系统时钟频率为11.0592MHz,那么通过UARTBAUD分频器来调整波特率的公式是:

UARTBAUD = 256 - FSYS / (16 * BaudRate)

在这个案例中,要获得9600波特率,我们可以计算出UARTBAUD的值:UARTBAUD = 256 - 11059200 / (16 * 9600) = 0xB8。这意味着在Verilog代码中,需要将UARTBAUD设置为这个十六进制值,以确保串口通信的正确速率。

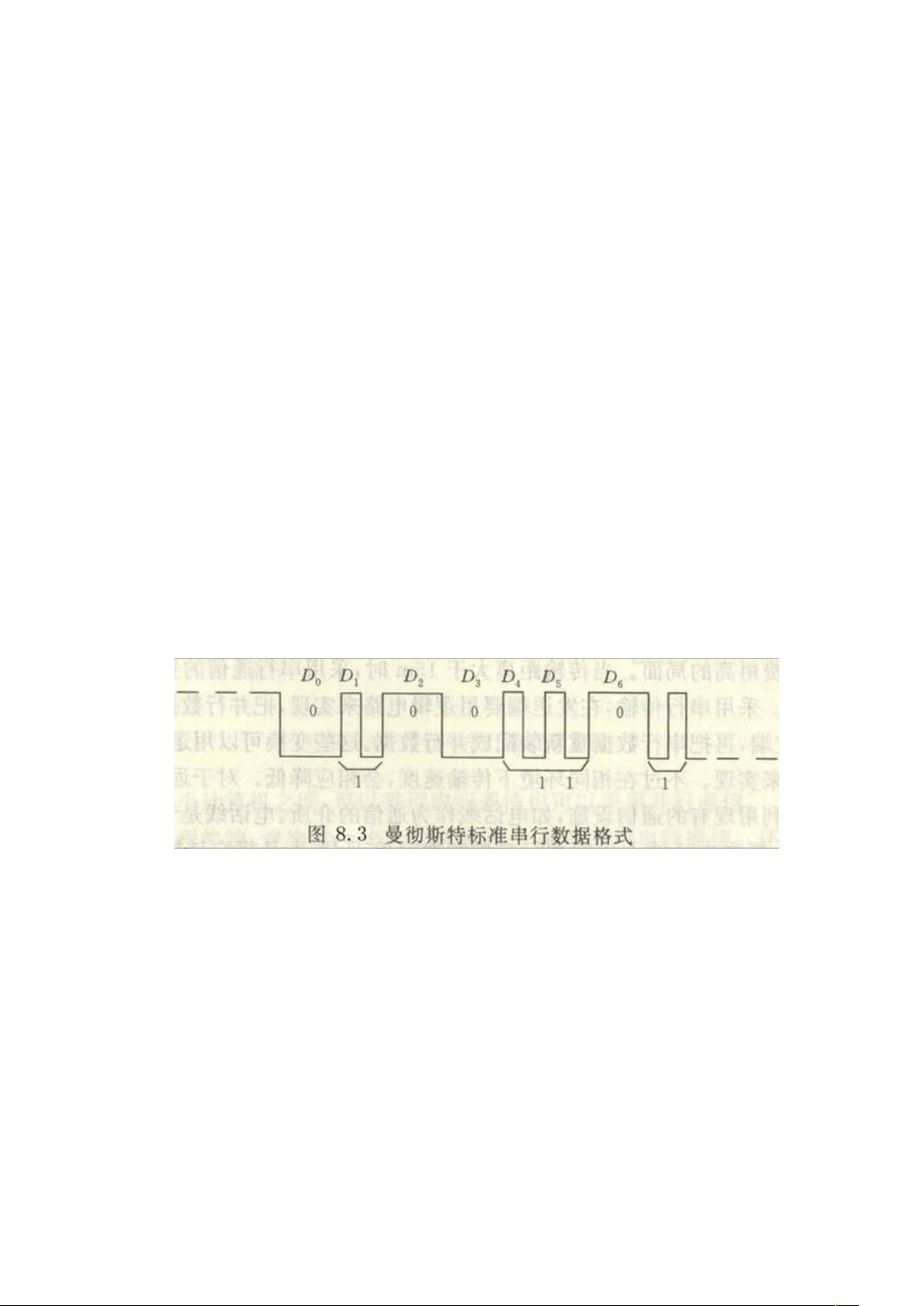

串行通信与并行通信相比,具有明显的优缺点。串行通信的优点在于节省传输线路资源,这对于远程通信和空间有限的应用场景至关重要。它只需要一条数据线即可进行位级的数据传输,降低了硬件复杂性和成本。然而,串行通信的缺点是数据传输效率较低,例如传送一个字节,相比于并行通信的1T时间,串行可能需要8T或更多的时间,这限制了它的速度和实时性。

串行通信适用于长距离、低速率的通信,如电话线通信或远距离的物联网设备通信,而并行通信则更适合短距离、高速率的数据交换,如本地计算机之间的快速通信。在实际应用中,设计师需要根据具体需求和环境来选择合适的通信方式。

FPGA波特率发生器作为串口通信中的重要部分,通过精确计算和编程实现,能够灵活调整串口的波特率,满足不同应用场景的需求。而在设计和实现过程中,理解串行通信的基本原理及其特点,以及如何利用Verilog等高级语言进行硬件描述,是至关重要的技能。

2014-06-13 上传

2022-09-24 上传

2012-10-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

gaoleiooo

- 粉丝: 0

- 资源: 21

最新资源

- 老师愿您开心每一天flash动画

- Globalize your Delphi applications without troubles

- ChickenVR-launcher:[已弃用] Chicken VR的启动器

- card-animation:简单的卡片动画

- bio331_2021:2021年生物信息学的注释和代码

- 投诉人:Accuser是一个轻量级的框架包装程序,可让您编写Github机器人来监视“拉取”请求并将人员分配给PR

- mkb:合作知识提炼嵌入知识库

- my-personal-site.io

- com_helloworld:创建组件是为了了解创建Joomla组件的过程

- Talent Eye Beta-crx插件

- vdrift:VDrift源代码

- addupstream:一个小的cli,可自动将上游遥控器添加到git项目中

- JSON2.jl:使用Julia类型快速进行JSON编组

- 毕业设计&课设-该项目旨在使移动机械手youBot从初始配置中拾取立方体并将其运输到所需的位置….zip

- Outils de productivité Rakuten-crx插件

- terrafirma:用于Terraform计划的静态分析工具