飞思卡尔MCU的IIC总线通讯教程

需积分: 9 132 浏览量

更新于2024-07-21

1

收藏 261KB PDF 举报

"飞思卡尔IIC总线的使用指南"

飞思卡尔(现NXP半导体)的应用笔记AN3291详细介绍了如何在飞思卡尔微控制器(MCU)上利用IIC(Inter-Integrated Circuit)总线进行通信,特别是主从模式下的通信。IIC总线通常用于MCU与IIC外围设备如串行EEPROM之间的通讯,虽然它也能直接连接两个MCU,但若需此类通信,SPI总线可能是更好的选择。

**1. 引言**

该应用笔记首先引入了IIC总线的概念,并指出其在主从模式中的应用。示例中,主模式的MCU将与串行EEPROM进行通信,而更换其他IIC设备时,只需修改对应从设备的IIC地址。

**2. IIC总线概述**

2.1 **IIC总线术语**

这部分解释了IIC总线的基本术语,如数据线(SDA)和时钟线(SCL),以及总线上的各种状态。

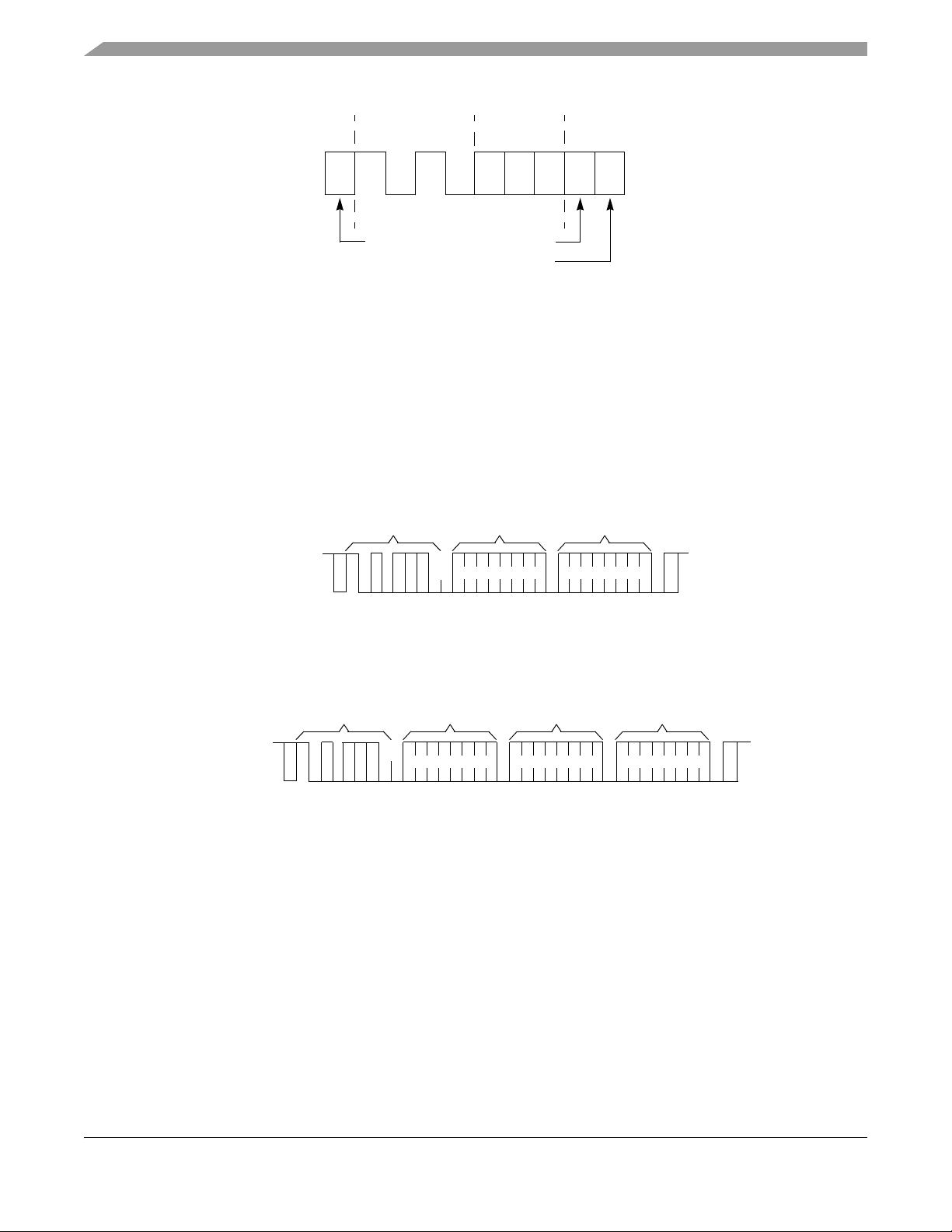

2.2 **位传输**

详细描述了数据通过IIC总线的单个位传输过程,包括数据线的高低电平变化。

2.3 **启动(START)和停止(STOP)条件**

定义了开始和结束通信的特定信号序列,即START条件(SCL高时SDA由高变低)和STOP条件(SCL高时SDA由低变高)。

2.4 **总线通信**

说明了在START和STOP条件之间,MCU如何通过SCL和SDA线与从设备交换数据。

2.5 **控制字节**

控制字节包含了目标设备的7位地址以及读写方向信息(第8位)。

2.6 **地址字节**

接着详细解释了如何构造和发送设备地址字节以选择特定的从设备。

2.7 **应答**

描述了从设备确认接收到数据或地址的应答机制,即SDA线上的低电平脉冲。

2.8 **读/写格式**

解释了在读取和写入操作中,数据在总线上的传输格式。

**3. IIC软件程序对于MCU**

3.1 **初始化**

提供MCU端IIC模块的初始化步骤,包括设置时钟频率、配置中断和设置从设备地址等。

3.2 **其他例程**

可能包括发送START条件、发送STOP条件、发送数据、接收数据、处理应答等低级IIC通信函数的实现。

这个文档为开发者提供了使用飞思卡尔MCU的IIC模块进行通信的实际操作指导,无论是在读取还是写入操作中,都有详细的步骤和注意事项。对于需要使用IIC总线的嵌入式系统设计者来说,是十分宝贵的参考资料。

2022-09-23 上传

2024-11-04 上传

2024-11-04 上传

2024-11-04 上传

2023-05-09 上传

2024-11-01 上传

2023-07-27 上传

liuning477

- 粉丝: 0

- 资源: 2