深入解析ARM的AXI总线协议

需积分: 34 161 浏览量

更新于2024-07-15

收藏 1.68MB DOCX 举报

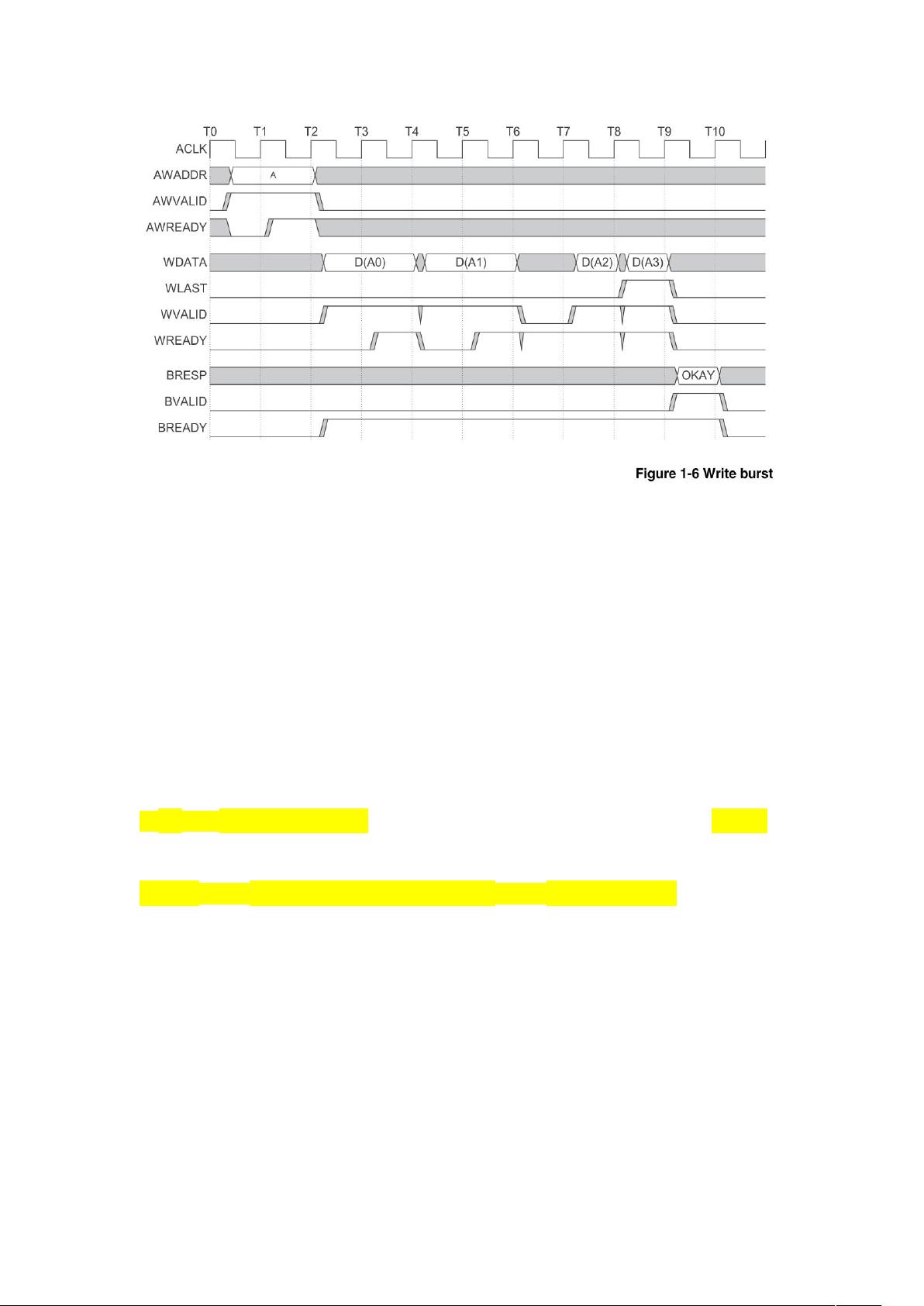

"AXI总线协议是ARM公司提出的AMBA 3.0协议的重要组成部分,是一种面向高性能、高带宽和低延迟的片内总线协议。它具有单向通道体系结构,支持不对齐的数据传输,独立的地址和数据通道,以及并发的突发操作,提升了数据吞吐能力和时序优化的可能性。AXI总线包含5个独立的通道:read address channel、write address channel、read data channel、write data channel和write response channel,每个通道都有VALID和READY握手机制,以及LAST信号来标记事务的结束。地址通道传输事务的地址和控制信息,读数据通道传递设备到主机的读取数据和响应,写数据通道则用于主机到设备的写入数据,并通过byte lane标识有效字节。"

AXI总线协议的详细分析:

AXI协议的设计旨在满足现代高性能系统-on-chip (SoC) 的需求,其核心特点是单向通道架构,这意味着信息仅在一个方向上传输,减少了时钟域间桥接的复杂性和延迟,降低了门数量,从而有助于降低功耗。此外,AXI协议支持不对齐的数据传输,使得数据交换更加灵活,适应各种内存布局。

AXI协议的另一个关键特性是其并行处理能力。通过支持多个并发突发操作,AXI能够在短时间内处理大量数据,显著提高了系统的数据吞吐率,这对于高速缓存、内存访问以及大规模数据处理等应用场景至关重要。此外,独立的地址和数据通道允许设计者对每个通道进行单独优化,可以提高时钟频率,降低延迟,以实现最佳性能。

在AXI协议的事务结构中,读取和写入事务都包含各自的地址通道,分别携带必要的地址和控制信息。例如,读取事务的结构包括读取地址通道,用于发起读取请求;读取数据通道则用于传输从设备返回的读取数据和响应信息,其中读响应信息表明读取操作是否成功。写入事务的结构类似,但包括写入地址通道,用于指定写入位置,以及写入数据通道,用于传输主机到设备的数据,每个写入数据包都带有byte lane信息,用于指示哪些字节数据有效。写响应通道则提供设备对写入事务的确认或反馈。

AXI协议中的VALID和READY握手机制是其高效通信的关键。信息源通过VALID信号通知接收端数据有效,而接收端通过READY信号表示已准备好接收数据,这样的同步方式确保了数据传输的准确性和效率。LAST信号则指示当前传输的最后一个数据,有助于正确解析事务边界。

AXI总线协议以其高效的通道设计、并发操作和灵活的数据传输能力,成为FPGA和SoC设计中实现高性能片内通信的标准。它不仅提升了系统的数据吞吐率,还降低了延迟,使得复杂系统设计变得更加可行,满足了现代计算和通信应用的苛刻要求。

755 浏览量

967 浏览量

491 浏览量

2022-01-23 上传

799 浏览量

234 浏览量

2021-11-28 上传

878 浏览量

163 浏览量