VHDL实现洗衣机控制系统

"洗衣机的vhdl设计"

在数字电子技术的学习中,VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种用于硬件描述的语言,广泛应用于 FPGA(Field-Programmable Gate Array)和 ASIC(Application-Specific Integrated Circuit)设计。本资料主要介绍了如何使用VHDL设计一个模拟洗衣机操作的系统,旨在帮助学生理解和应用VHDL。

一、设计任务及要求

设计任务是创建一个基于VHDL的洗衣机控制模型,这个模型应该能够模拟洗衣机的基本功能,如启动、暂停、定时以及显示当前状态。具体要求包括定义合适的输入输出接口,如启动按钮、暂停按钮、定时设置等,并设计相应的逻辑电路来处理这些输入,同时通过显示器输出洗衣机的工作状态。

(一)具体要求

1. 设计一个能够接收用户输入(如启动、暂停、定时)的接口。

2. 设计内部计时机制,以模拟洗涤过程的持续时间。

3. 实现计时结束后的自动停机或提示功能。

4. 提供清晰的用户界面(如LED显示器),显示当前工作状态和剩余时间。

(二)输入输出资源说明

- 输入:启动按钮(START)、暂停按钮(PAUSE)、定时设置(TIMER_SET)。

- 输出:状态指示灯(如运行、暂停、完成)、显示器(DISPLAY)。

二、设计原理与方案

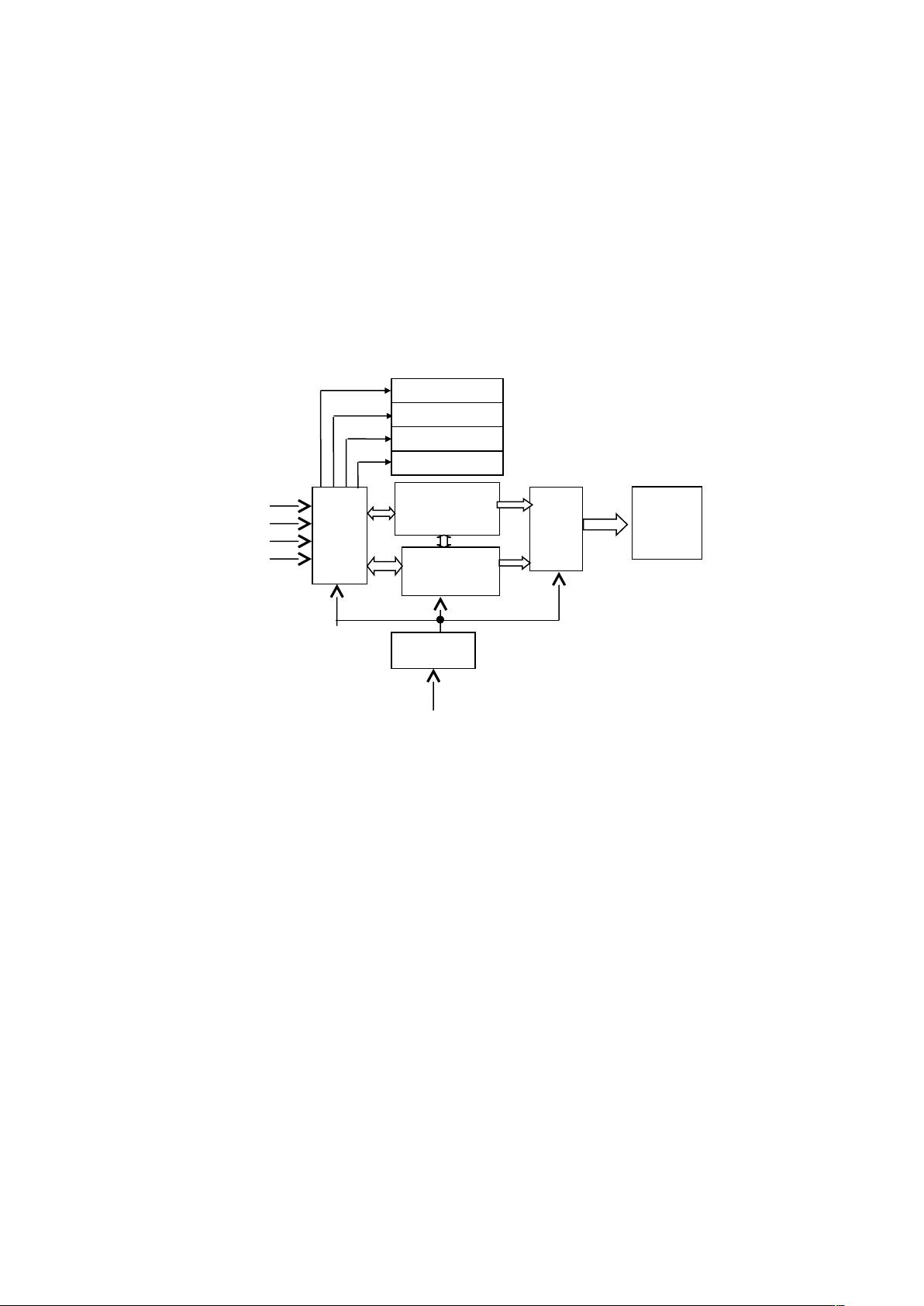

(一)顶层设计方案

顶层设计是整个洗衣机系统的总览,它将包含所有子模块(如分频器、计时器、显示器和控制逻辑)的接口,通过综合这些子模块来实现整个洗衣机的逻辑功能。

(二)分频器设计方案

分频器用于将时钟信号进行分频,以生成适合计时器使用的慢速时钟。这可以通过计数器实现,当计数值达到预设值时,输出一个脉冲,用于触发计时器的递减计数。

(三)计时器(倒计时)设计方案

计时器采用递减计数器结构,根据设定的时间和分频器提供的时钟信号,逐次减小计数值,直到达到零,表示定时结束。

(四)显示器设计方案

显示器可能由7段LED驱动电路构成,用来显示剩余时间或当前状态,可以通过译码器将计数值转换为7段码显示。

(五)暂停设计方案

暂停功能需要在接收到暂停信号时,停止计时器的计数,并保持当前显示状态,直到接收到恢复信号,计时继续。

三、电路设计、仿真与实现

这部分详细讲解了如何使用VHDL编写上述各个模块的代码,并进行仿真验证。设计实现包括顶层模块的连接,以及分频器、计时器、显示器和控制逻辑的实例化和参数配置。

通过实际的电路设计和仿真,学生可以直观地看到VHDL代码如何转化为实际的硬件行为,理解数字系统设计的基本流程。这样的实践项目有助于提高学生的逻辑思维能力,以及对VHDL语言的掌握。

2011-07-17 上传

2009-10-02 上传

2022-09-22 上传

2023-09-23 上传

2023-05-16 上传

2023-12-16 上传

2023-12-30 上传

2023-06-10 上传

2023-07-31 上传

xiaoaiaishanshan

- 粉丝: 0

- 资源: 1

最新资源

- 水利水电施工组织设计-临沂滨河大道工程施工组织设计方案

- LoveLink.rar

- ant-design-vue-4.1.0.zip

- scolear.github.io

- Python实现的番茄网小说下载器源代码,利用requests库采集和parsel库进行解析,然后用用tkinter做了UI

- 采用MSP430FG437微控制器 (MCU) 设计的脉动式血氧计-电路方案

- SD8227_hw刷机固件及说明.zip

- Excel-VBA实用技巧范例-用户窗体高级操作技巧.zip

- MATLAB数据字典生成代码-dsc-0-03-03-introducing-python-libraries-online-ds-pt-02

- 易语言读取windows序列号源码

- 一键搜索处理您手机中的重复文件 释放存储空间 .rar

- ant-design-vue-3.2.3.zip

- elastic-training-repo:数据集,泊坞窗组成的文件,注释以及与Elastic Stack相关的其他内容的集合

- matlab手写卷积神经网络人脸识别.zip

- Python从安居客获取某城市的所有新房和二手房源信息源代码(小区挂牌价、物业类型、竣工时间、总户数、总面积等)生成csv数据

- 基于QT实现的工资管理系统.rar