Xilinx Vivado HLS:C语言实现FPGA设计入门

需积分: 13 51 浏览量

更新于2024-07-23

1

收藏 11.52MB PDF 举报

"Vivado 高层综合是Xilinx公司提供的一种高级综合软件,它能够将用C、C++或SystemC编写的规范转换成寄存器传输级(RTL)实现,进而综合进Xilinx的现场可编程门阵列(FPGA)。此工具主要应用于Vivado Design Suite 2014.1和2014.2版本。文档包含了Vivado HLS的基础知识、使用方法以及最新的HLS UltraFast设计方法学。"

Vivado 高层综合(High-Level Synthesis, HLS)是Xilinx开发的一款强大的工具,旨在加速FPGA设计流程。它允许工程师使用高级语言(如C、C++和SystemC)来描述硬件功能,相比于传统的硬件描述语言(如Verilog和VHDL),这种方式更接近于软件开发的思维方式,提高了设计效率和易读性。

1. **高级语言设计的优势**

- **易读性**:C/C++语法简洁明了,使得设计逻辑更易于理解和维护。

- **复用性**:可以利用已有的C库和算法,减少设计工作量。

- **快速迭代**:高级语言的编译和仿真速度远快于硬件描述语言,便于快速验证设计。

2. **Vivado HLS的工作流程**

- **代码输入**:用户使用C、C++或SystemC编写设计规格。

- **代码优化**:HLS工具对源代码进行分析和优化,转换为RTL级逻辑。

- **IP核生成**:生成的RTL代码可以作为Vivado中的IP核,用于后续的布局和布线。

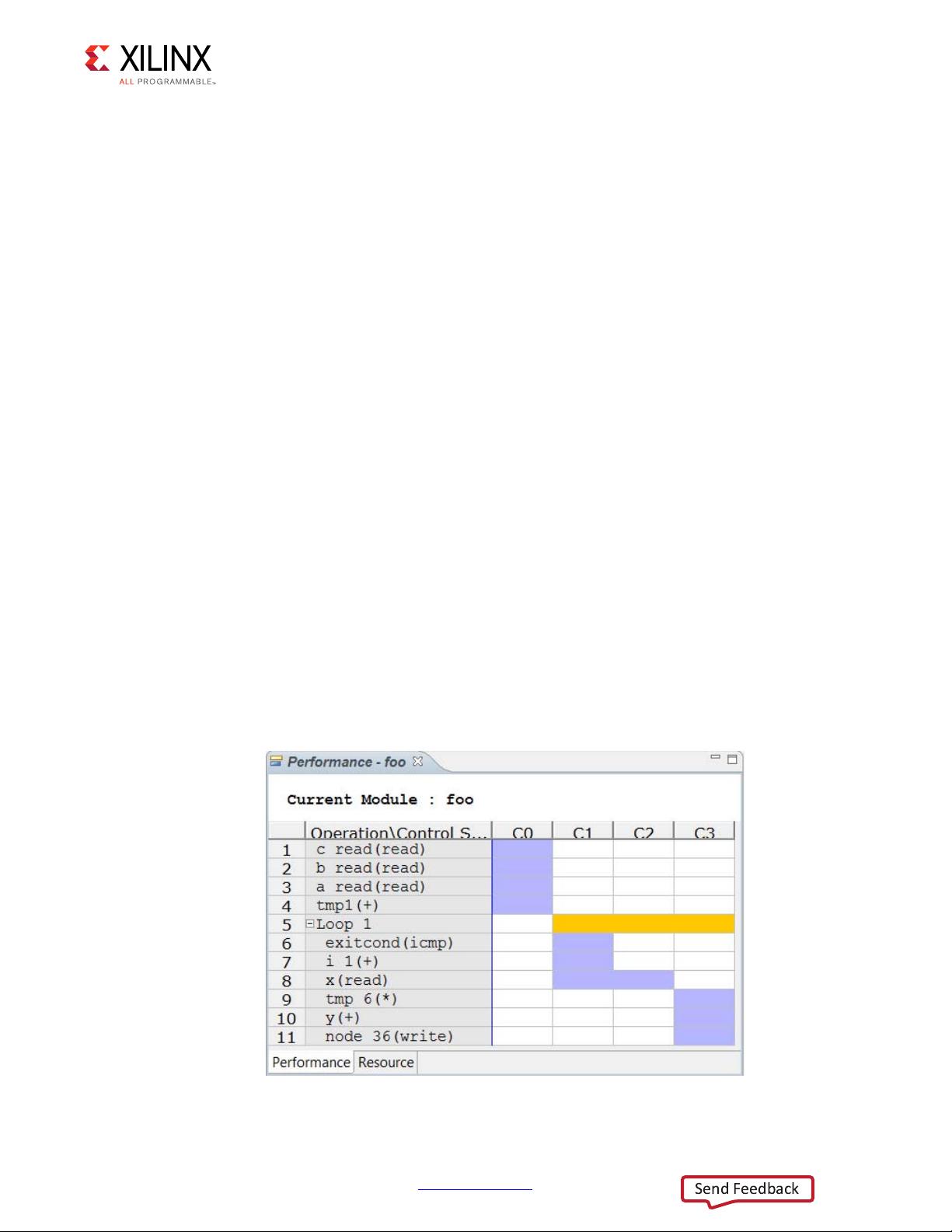

- **性能评估**:提供时序、功耗和面积等关键指标的估计,方便调整优化策略。

3. **HLS UltraFast设计方法学**

- 这是一种推荐的设计和调优流程,旨在最大限度地提高设计性能和效率。

- 包括了代码优化技巧、并行化策略、资源分配和约束设置等方面的指导,帮助用户更快地达到设计目标。

- 提供了自动化工具和预定义模板,简化了设计流程。

4. **使用Vivado HLS**

- 用户需要了解基本的HLS指令和语法,例如pragma声明,用于指导合成过程。

- 设计者需要设定性能目标和资源限制,并通过实验和迭代来优化设计。

- 通过HLS的仿真功能,可以在代码级别验证设计行为,确保功能正确性。

5. **版本适用性**

- 文档适用于Vivado Design Suite 2014.1和2014.2,这意味着某些特性或工具可能不适用于其他版本。

6. **持续更新与反馈**

- 文档经过多次修订,以适应工具的改进和新特性的添加。

- 用户可以通过指定渠道提供反馈,以促进工具的进一步完善。

Vivado HLS是FPGA设计的一个强大工具,它简化了设计流程,提高了开发效率,同时提供了高级语言的便利性和灵活性。通过掌握HLS技术,开发者可以更高效地利用Xilinx FPGA平台,实现高性能、低功耗的定制化硬件解决方案。

258 浏览量

2018-08-10 上传

2024-12-25 上传

h_yuan03

- 粉丝: 0

- 资源: 1

最新资源

- 基于KNN算法的婚恋推荐算法研究.zip

- Animate.css-Tutorial:Animate.css教程的文件

- android应用源码动画文字自由移动-IT计算机-毕业设计.zip

- roadtrip-node:使用 node 和 mongo-db 的 roadtrip 应用程序

- TemplatesNetCore:我用于快速构建应用程序的代码模板,这些模板具有我在项目中通常使用的实践,特性和库

- WeatherWebApiSample

- mrobinson93.github.io:网站

- 数据库设计project——物业集团管理系统.zip

- Enterprise_Application_Solution:免费资料和样品

- porgy:Protoc插件

- V5:分层排队网络求解器

- dltmatlab代码-event-driven-IP:用于尖峰神经网络的事件驱动的内在可塑性(IP)学习规则

- MMath-Code:机器学习和微分方程

- testDBJenkins

- LunarCalendar:一个基于 Electron + React + Material Design 的工具栏日历,适用于 Mac、Windows 和 Linux

- dltmatlab代码-3D-DIC:3D-DIC