Quartus II 13.1 FPGA开发教程:半加器实现

24 浏览量

更新于2024-08-29

1

收藏 1.81MB PDF 举报

"这篇教程详细介绍了使用Quartus II 13.1开发FPGA项目的过程,以半加器的设计为例。"

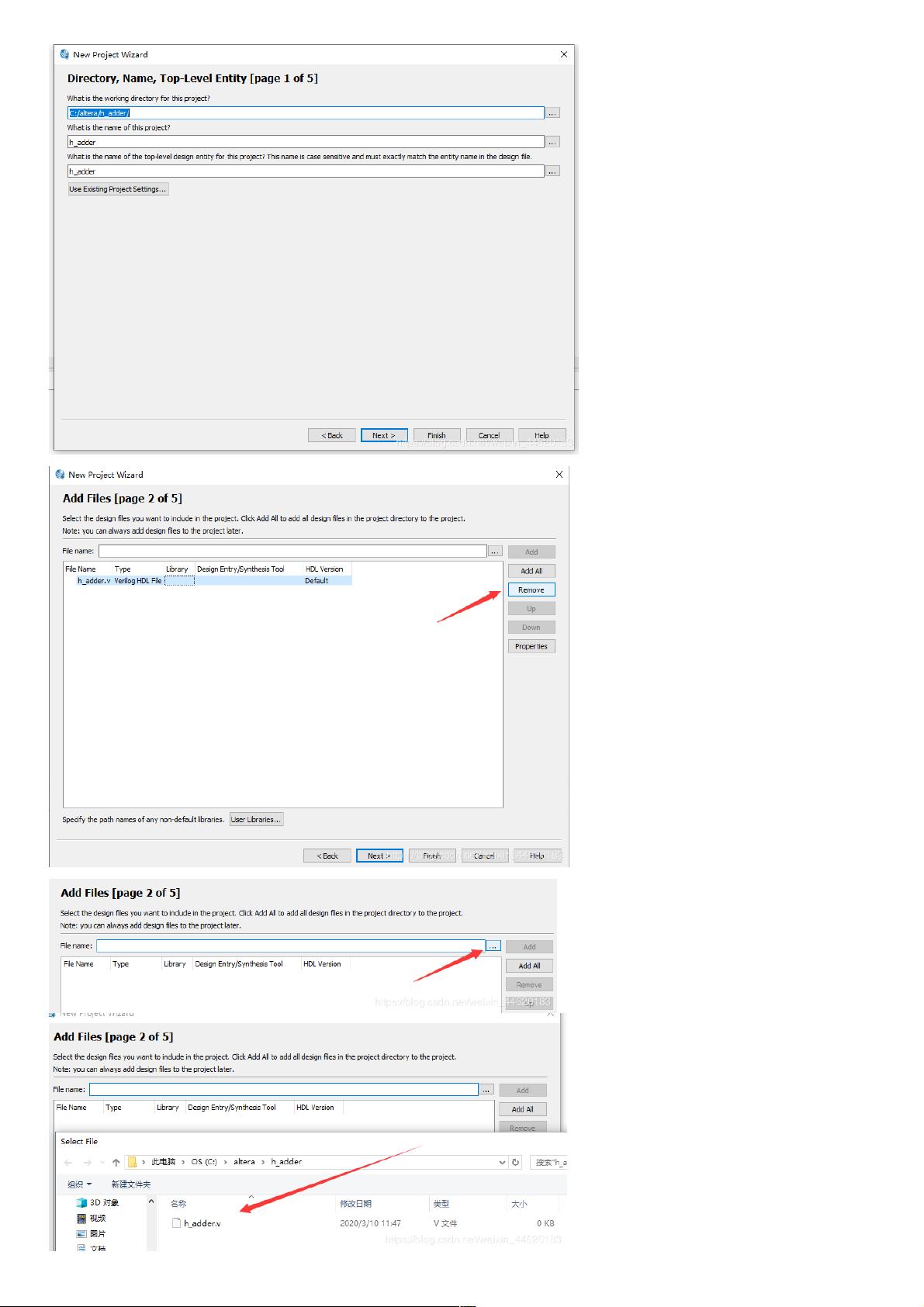

在FPGA设计中,Quartus II是一款常用的开发工具,本教程以13.1版本为背景,通过创建半加器的Verilog程序来演示完整的开发流程。首先,你需要新建一个文件夹作为项目存储位置,接着创建一个新的Verilog文件。在文件中编写半加器的Verilog代码,半加器是一个基本的数字逻辑电路,它将两个单比特输入相加并产生一个和位以及一个进位位。

新建Verilog文件后,将其保存到刚才创建的文件夹,并在Quartus II中新建工程。在创建工程时,确保工程名称与顶层实体的名称一致,这是为了保持项目的整洁和一致性。然后,移除工程中预设的文件,添加刚刚创建的Verilog源文件。接下来,选择目标FPGA器件,这里可能是Altera的某款芯片,例如Cyclone或Stratix系列。

在设置编译选项时,可以选择启用SmartComplication以优化编译速度。完成配置后,执行编译操作,检查是否有错误或警告。编译无误后,进入ModelSim仿真环境的设置。在Quartus II中,通过Tools -> Options设置链接路径,确保没有语法错误,特别是路径中的反斜杠要正确添加。

接下来,Quartus II会自动生成仿真模板(vt文件)。你需要在模板中添加必要的初始化值和时间单位,完成对testbench的编写。然后,在Assignments -> Settings中设置ModelSim调用的相关参数,将testbench文件添加到工程中。

最后,启动ModelSim进行仿真。在首次打开时,可能需要调整波形视图的缩放,以便清晰地看到信号的变化。通过观察仿真波形,可以验证半加器设计的功能是否正确。这个过程对于理解和掌握FPGA开发流程至关重要,同时也为后续更复杂的设计打下了基础。

总结来说,本教程详细讲述了使用Quartus II 13.1和ModelSim进行FPGA设计的步骤,包括项目创建、代码编写、编译、设置及仿真,特别适合初学者参考学习。通过实践这个半加器的例子,学习者能更好地理解FPGA开发工具的使用方法和数字逻辑电路的Verilog实现。

2021-02-23 上传

2023-09-09 上传

2023-08-30 上传

2023-09-01 上传

2023-07-25 上传