VHDL实现的24小时制带复位功能数字时钟设计

需积分: 9 139 浏览量

更新于2024-11-01

收藏 525KB DOCX 举报

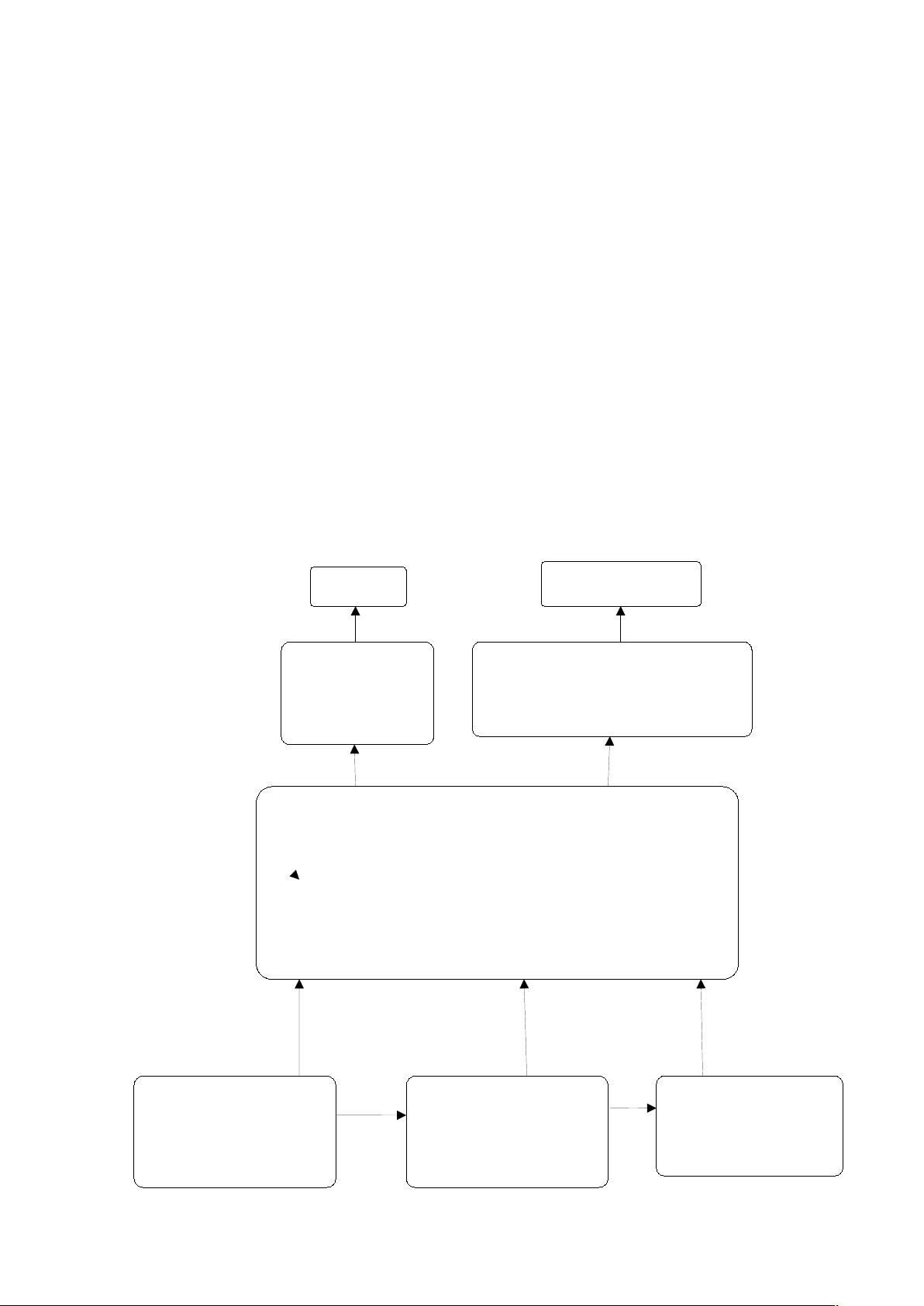

"该资源是关于使用EDA工具和VHDL语言设计一个具有复位功能的24小时制数字时钟的实践项目。设计中包含了60进制的秒计数器、60进制的分计数器以及24进制的时计数器,每个计数器都连接到相应的7段LED数码显示管进行时间显示。通过复位和进位信号,各个计数器协同工作,实现时间的准确递增。"

在数字时钟设计中,EDA(Electronic Design Automation)技术是核心工具,它可以帮助工程师在硬件级别上描述和验证数字系统。VHDL(VHSIC Hardware Description Language)是一种广泛使用的硬件描述语言,允许设计者以结构化的方式描述电路的行为和结构。在这个项目中,VHDL被用来编写计数器和选择器等基本逻辑单元的代码。

首先,设计包含了一个60进制的计数器counter60,它负责秒的计数。这个计数器有四个输出位(X和Y),一个进位输出(CO)和一个复位端(RST)。当复位信号为高时,计数器将被重置。计数器的时钟信号(CLK)输入用于控制计数过程,而进位输出则传递给下一级计数器,即分钟计数器。

分钟计数器也是60进制的counter60实例,但其复位信号与秒计数器的复位端相连,时钟输入则连接到秒计数器的进位输出,这样每当秒计数器完成一次循环,分钟计数器就会增加一。

接着,设计包含一个24进制的计数器counter24,用于表示小时。这个计数器同样有复位端和时钟输入,但它的时钟输入来自分钟计数器的进位输出,确保小时的递增基于分钟的完整计数周期。counter24也有四个输出位,用于显示小时。

为了将这些计数器的输出显示在7段LED数码管上,需要一个6选1选择器(MUX)和LED显示译码器。选择器根据时间计数器的输出选择当前需要显示的时间段,其输出连接到译码器,译码器将四位二进制数转换为驱动7段LED的段选信号。同时,选择器的另外三位输出连接到3-6译码器,产生位选信号,用于驱动数码管的特定位置。

设计框架中还包括了时钟脉冲计数器,它的输出用于选择当前要显示的时间段,实现数码管的正确位选。整个设计通过这种方式实现了完整的24小时制数字时钟功能,包括小时、分钟和秒的精确显示,并且具备复位功能,能够在系统启动或需要时重置时间。

这个项目不仅展示了VHDL编程的基本概念,还涵盖了数字逻辑设计中的计数器、选择器、译码器等关键组件的使用,以及如何将它们整合到一个实际应用中,是学习数字系统设计和EDA技术的优秀实践案例。

3108 浏览量

点击了解资源详情

167 浏览量

2013-01-02 上传

154 浏览量

2010-04-11 上传

448 浏览量

1629 浏览量

1648 浏览量

hudadexuesheng

- 粉丝: 0

- 资源: 3

最新资源

- win_udp:Windows网络udp框架服务器和侦听器

- 如何规划团队训练课程PPT

- torch_cluster-1.5.5-cp36-cp36m-linux_x86_64whl.zip

- 取Excel表格有数据单元格的起讫行列.rar

- zencharts:将 High Charts 库的强大功能与 Zendesk Developer API 相结合的小型应用程序

- wild-rydes:野生莱德

- Redosnap Launcher-crx插件

- CNN_for_brain_ventricles_segmentation:“个人3D脑图集”项目。 利用全卷积神经网络对大脑的CT数据进行分割

- 批量修改文件名.zip

- 取Excel表格有数据单元格的起讫行、列.rar

- html2text:用 Go 编写的 html 到文本转换器

- torch_scatter-2.0.4-cp37-cp37m-win_amd64whl.zip

- Email Notifier-crx插件

- yun-text:“云杯”景区声誉评价得分预测中第三个解决方案的DL部分

- milestoneproject2-memorygame:一种记忆游戏,要求用户匹配隐藏在牌组中的成对纸牌

- Android Binder通信案例