TEC-4计算机组成原理实验系统:8位模型与教学实践

95 浏览量

更新于2024-06-28

收藏 1.3MB DOC 举报

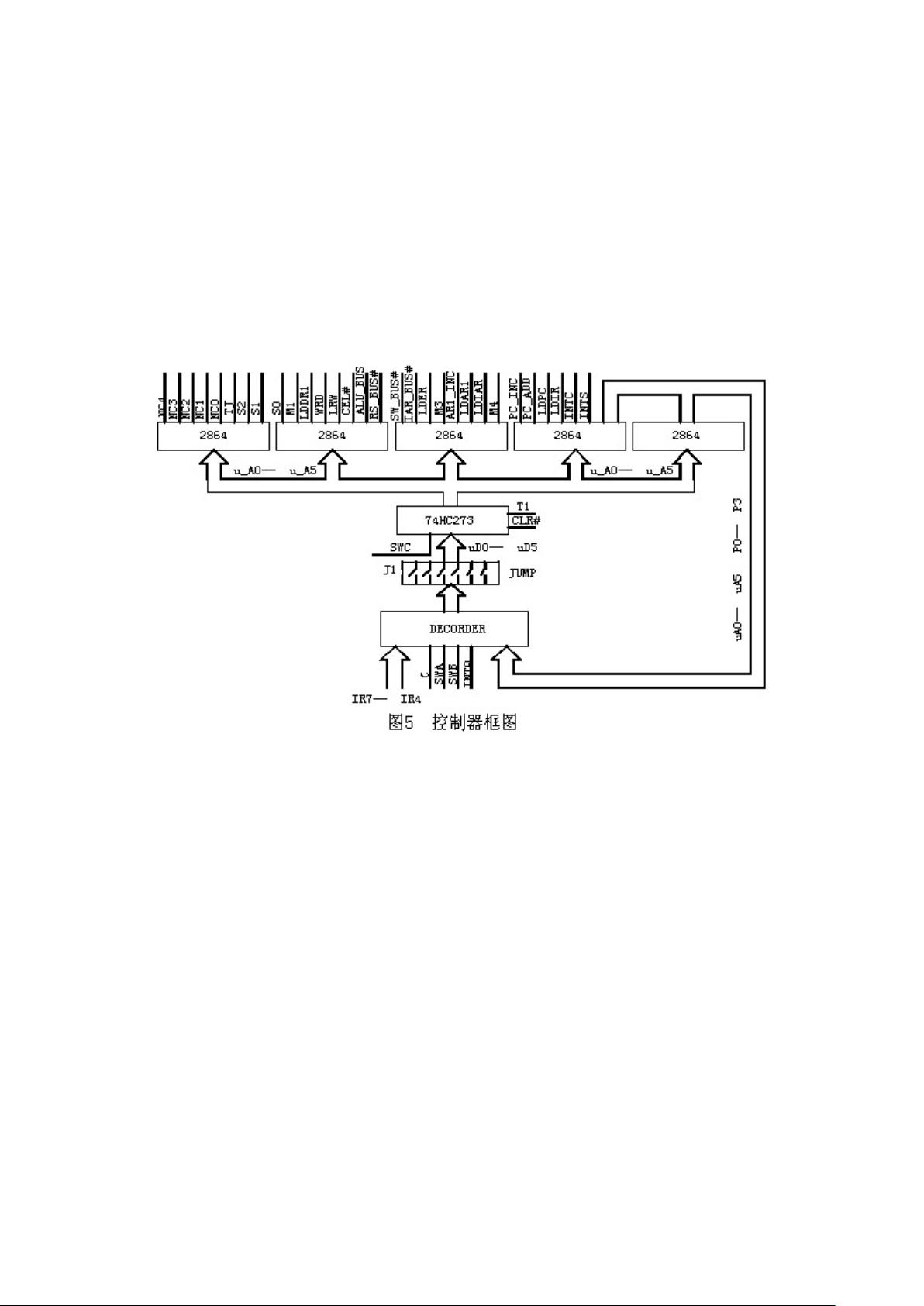

"TEC-4计算机组成原理实验系统是一套专为计算机组成原理和计算机系统结构课程设计的实验平台,由邮电大学计算机学院、清华同方教学仪器设备公司和拓普威电子技术联合研发。该系统的特点鲜明,主要包括以下几个方面:

1. 系统构成:系统由控制台、数据通路、控制器、用户自选器件试验区、时序电路和电源部分组成,每个部分都具备实际操作和学习的价值。

2. 硬件设计:系统采用8位计算机模型,具备数据总线和指令总线双总线结构,支持流水线控制,有助于理解计算机内部的并行工作原理。控制器提供微程序控制器和硬布线控制器两种类型,分别对应不同的设计策略,如流水线和非流水线,增加了实验的灵活性。

3. 核心组件:核心部件包括ispLSI1016寄存器堆和ispLSI1024运算器,这些高度集成的芯片展现了现代集成电路技术的应用,增强了学生的实践动手能力。

4. 实验功能:系统支持多种实验,如运算器组成、双端口存储器、数据通路设计、微程序控制器开发、中断处理、CPU结构分析、机器指令执行等,涵盖了计算机组成原理的核心概念。

5. 电源管理:电源部分采用模块化设计,轻便且具有过载保护和抗短路功能,确保安全稳定供电。

6. 易用性:采用自锁紧累接接线方式,接线简洁明了,便于学生进行实验操作。

7. 时序控制:系统内嵌有1MHz晶体振荡器和GAL22V10等元件组成的时序发生器,为计算机模型提供精确的时间控制,帮助学生理解指令执行的时序逻辑。

通过TEC-4计算机组成原理实验系统,学生可以亲自动手操作,深入理解计算机的各个组件如何协同工作,从而提升计算机系统设计和分析的能力。这套系统适合大专、本科和研究生层次的学习,是培养理论与实践相结合的优秀计算机人才的重要工具。"

点击了解资源详情

214 浏览量

241 浏览量

2021-09-29 上传

379 浏览量

2021-10-06 上传

2022-03-03 上传

147 浏览量

matlab大师

- 粉丝: 2791

- 资源: 8万+

最新资源

- C++ XML.pdf

- Java连接Oracle数据库的各种方法.doc

- Windows+API一日一练

- Linux命令集合.doc

- Linux系统指令大全

- 数据库系统概论习题答案

- solaris多线程编程指南

- 中文版AutoCAD_2007实用教程.

- linux指令大全(值得一看)

- ping命令的使用,ping

- 解密深入浅出ARM7-LPC213x_214x(上).pdf

- C C++嵌入式编程.pdf

- 中文fm353 使用说明

- Photoshop大师之路

- MCITP:数据库管理人员认证相关信息

- Visual Speech Recognition with Loosely Synchronized Feature Streams