并行CRC计算:基于Verilog或VHDL的实现方法

需积分: 50 167 浏览量

更新于2024-09-10

收藏 387KB PDF 举报

"CRC并行实现方法"

CRC(循环冗余校验)是一种广泛应用于通信协议、数据存储和传输中的错误检测技术。它基于模2除法的原理,通过计算一个特定的多项式来生成一个校验码,这个校验码可以检测出数据中的单个或多个比特错误。在本文中,作者Evgeni Stavinov探讨了一种实用的并行CRC(Cyclic Redundancy Check)电路的生成方法,特别适用于根据任意CRC生成多项式定制的并行CRC电路设计。

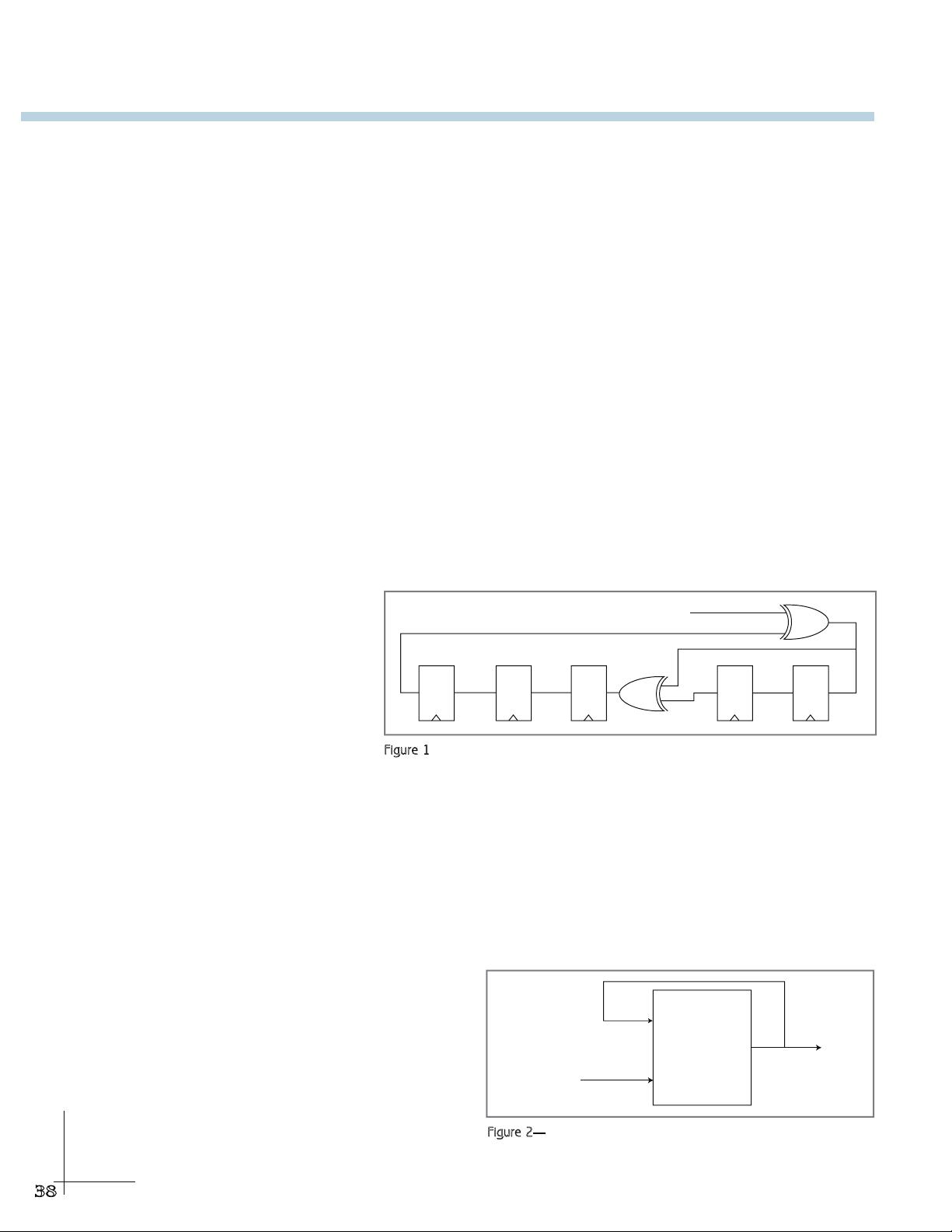

并行CRC实现通常比串行实现更快,因为它可以在多个时钟周期内同时处理多位数据。如图2所示,一个并行CRC电路包含一个M位CRC输入,一个M位CRC输出以及一个生成器,这个生成器对应于CRC的生成多项式。生成器用于确定从当前CRC状态到下一个CRC状态的转换,这依赖于输入数据和当前CRC值。

生成并行CRC代码的关键在于理解CRC生成多项式。例如,图1展示了一个USB CRC5实现,使用了生成多项式G(x) = x^5 + x^2 + 1。这个多项式定义了CRC的长度(在这种情况下是5位)以及如何计算CRC值。在并行实现中,每个时钟周期,生成器会根据输入数据和当前CRC状态更新CRC输出。

文章详细介绍了如何将这种理论转化为实际的硬件描述语言(Verilog或VHDL)代码。这种方法使得设计者能够快速为任何给定的多项式和数据宽度生成并行CRC电路。设计过程可能包括以下步骤:

1. **多项式选择**:首先,选择合适的CRC生成多项式,这会影响CRC的检测能力。不同的应用可能需要不同长度和特性的CRC。

2. **状态转移矩阵**:根据选定的生成多项式,计算出CRC状态的转移矩阵。这个矩阵描述了如何根据输入数据更新CRC状态。

3. **硬件描述**:将转移矩阵转换为Verilog或VHDL代码,构建逻辑门阵列实现CRC计算。这通常涉及逻辑优化,以减少门数量和延迟。

4. **仿真与验证**:设计完成后,使用仿真工具验证代码功能是否正确,确保其能按照预期检测数据中的错误。

5. **综合与实现**:最后,将设计综合进FPGA或ASIC芯片,进行物理实现和测试。

并行CRC生成方法的优点在于提高了计算效率,尤其在需要处理大量数据流的应用中,例如高速通信接口。然而,它也可能占用更多的硬件资源,因为并行结构需要更多的逻辑元件。因此,在实际应用中,需要权衡速度和硬件成本。

理解和掌握CRC并行实现方法对于电子和计算机工程师至关重要,特别是那些参与通信协议设计、嵌入式系统开发以及对数据完整性有高要求的项目。通过本文提供的方法,工程师们能够更加灵活地设计和定制适合特定需求的CRC电路。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-05-21 上传

点击了解资源详情

点击了解资源详情

2015-09-22 上传

点击了解资源详情

点击了解资源详情

YarayQin

- 粉丝: 24

- 资源: 3

最新资源

- 断路器操动机构实效测试仪器(黎斌)-已修改.doc

- Eclipse从入门到精通( 1,2)pdf版本

- 整数划分问题 将正整数n表示成一系列正整数之和:n=n1+n2+…+nk,其中n1≥n2≥…≥nk≥1,k≥1。

- Struts in Action 中文修正版.pdf

- XFire中文教程,webservice

- J2EE指南[pdf]

- 线性方程组高斯消元法

- dw_questions

- 图书管理系统DOC格式文件

- 活动安排问题 贪心算法

- WEP 密码破解教程

- 51单片机C语言编程实例

- 基于Matlab的遗传算法实现

- Apress.Pro.PHP.Patterns.Frameworks.Testing.and.More.Mar.2008

- ORACLE官方DBA中文版

- linux系统与应用程序的移植