没有合适的资源?快使用搜索试试~ 我知道了~

首页W5200芯片详细资料v1.2.7:嵌入式TCP/IP控制器设计指南

W5200芯片详细资料v1.2.7:嵌入式TCP/IP控制器设计指南

需积分: 10 7 下载量 55 浏览量

更新于2024-07-24

收藏 3.42MB PDF 举报

"W5200芯片资料_v1.2.7" 是一款针对嵌入式系统的硬线TCP/IP嵌入式以太网控制器,专为那些寻求简单易用且集成度高的互联网连接解决方案的用户设计。这款由WIZnet Co., Inc.开发的产品在版本1.2.7中提供了全面的文档支持。 W5200的主要特点是它集成了一个经过市场验证的完整TCP/IP堆栈,包括TCP、UDP、IPv4、ICMP、ARP和IGMP协议,以及PPP over Ethernet (PPPoE)功能。这种硬接线的设计使得在单个芯片上实现TCP/IP栈、10/100以太网MAC和PHY成为可能,简化了网络应用的开发过程。用户无需处理复杂的以太网控制器,只需通过简单的套接字编程即可实现所需功能。 内部数据通信内存为32K字节,这使得W5200具有足够的存储空间来支持实时的数据传输,尤其是在流量较高的应用环境中。此外,W5200采用串行外围接口(SPI)设计,便于与外部微控制器(MCU)轻松集成。其SPI支持高速通信能力,这意味着在硬件层面能够实现高效的数据交换,提高了系统的整体性能。 这款芯片特别适合于物联网(IoT)设备、工业自动化、消费电子等需要互联网连接但对体积和复杂性有限制的应用场景。它的设计目标是提供一个易于部署和维护的解决方案,帮助开发者快速实现基于网络的功能,同时保持系统小型化和成本效益。 总结来说,W5200芯片是一个强大的工具,它将复杂的网络协议处理内置于单一芯片,通过SPI接口简化了与其他控制单元的连接,为嵌入式系统提供了经济高效的互联网连接解决方案。无论是在家庭自动化还是工业监控中,W5200都能作为核心组件发挥关键作用。

资源详情

资源推荐

© Copyright 2012 WIZnet Co., Inc. All rights reserved.

14

iEthernet

W5200

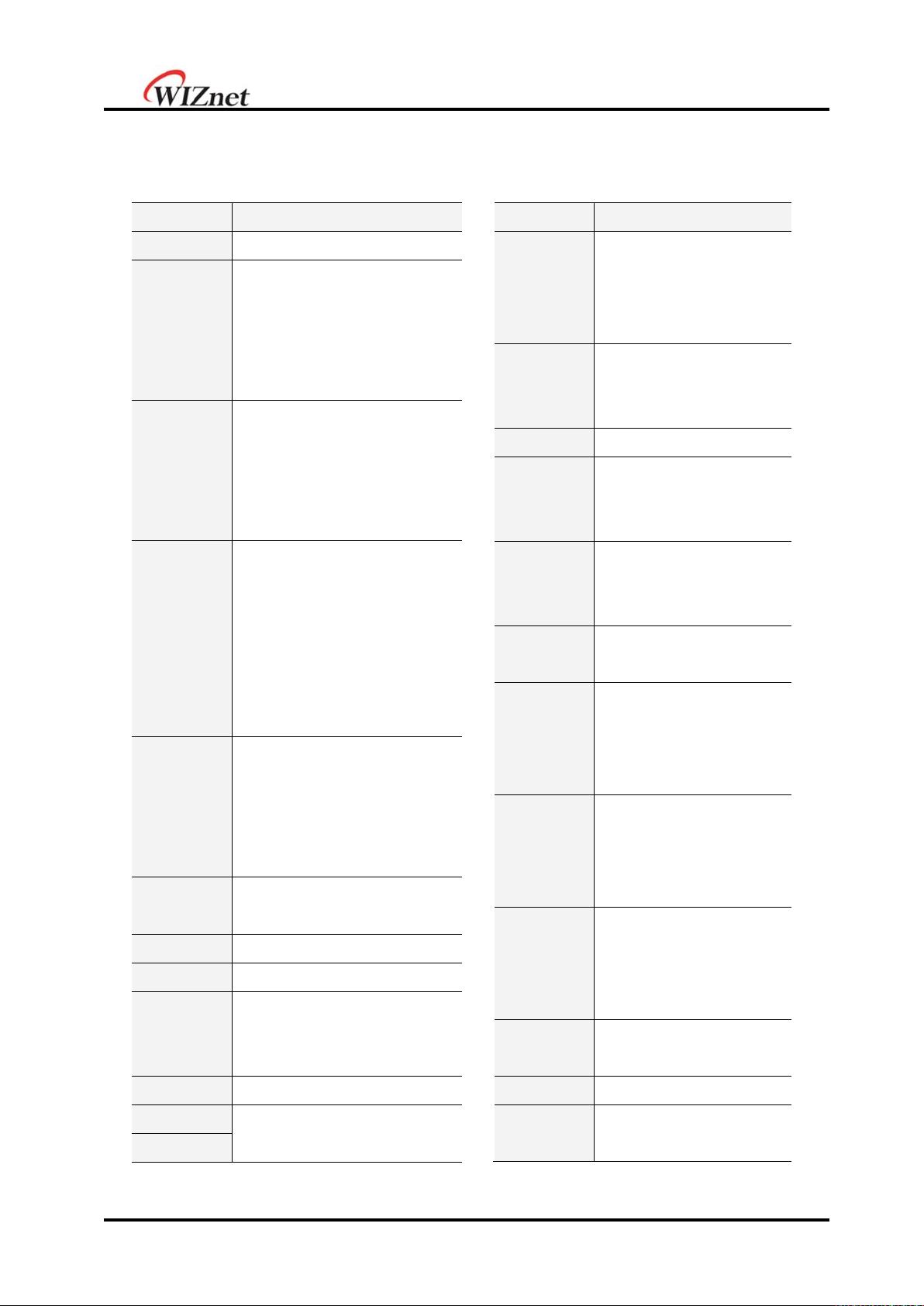

3 W5200 Registers

3.1 common registers

Address

Register

0x0000

Mode (MR)

0x0001

0x0002

0x0003

0x0004

Gateway Address

(GAR0)

(GAR1)

(GAR2)

(GAR3)

0x0005

0x0006

0x0007

0x0008

Subnet mask Address

(SUBR0)

(SUBR1)

(SUBR2)

(SUBR3)

0x0009

0x000A

0x000B

0x000C

0x000D

0x000E

Source Hardware Address

(SHAR0)

(SHAR1)

(SHAR2)

(SHAR3)

(SHAR4)

(SHAR5)

0x000F

0x0010

0x0011

0x0012

Source IP Address

(SIPR0)

(SIPR1)

(SIPR2)

(SIPR3)

0x0013

0x0014

Reserved

0x0015

Interrupt (IR)

0x0016

Interrupt Mask (IMR)

0x0017

0x0018

Retry Time

(RTR0)

(RTR1)

0x0019

Retry Count (RCR)

0x001A

Reserved

0x001B

Address

Register

0x001C

0x001D

Authentication Type

in PPPoE

(PATR0)

(PATR1)

0x001E

Authentication

Algorithm in PPPoE

(PPPALGO)

0x001F

Chip version(VERSIONR)

0x0020

~

0x0027

Reserved

0x0028

PPP LCP

RequestTimer

(PTIMER)

0x0029

PPP LCP Magic

number (PMAGIC)

0x002A

~

0x002F

Reserved

0x0030

0x0031

Interrupt Low Level

Timer

(INTLEVEL0)

(INTLEVEL1)

0x0032

~

0x0033

Reserved

0x0034

Socket Interrupt

(IR2)

0x0035

PHY Status(PSTATUS)

0x0036

Socket Interrupt

Mask (IMR2)

© Copyright 2012 WIZnet Co., Inc. All rights reserved.

15

iEthernet

W5200

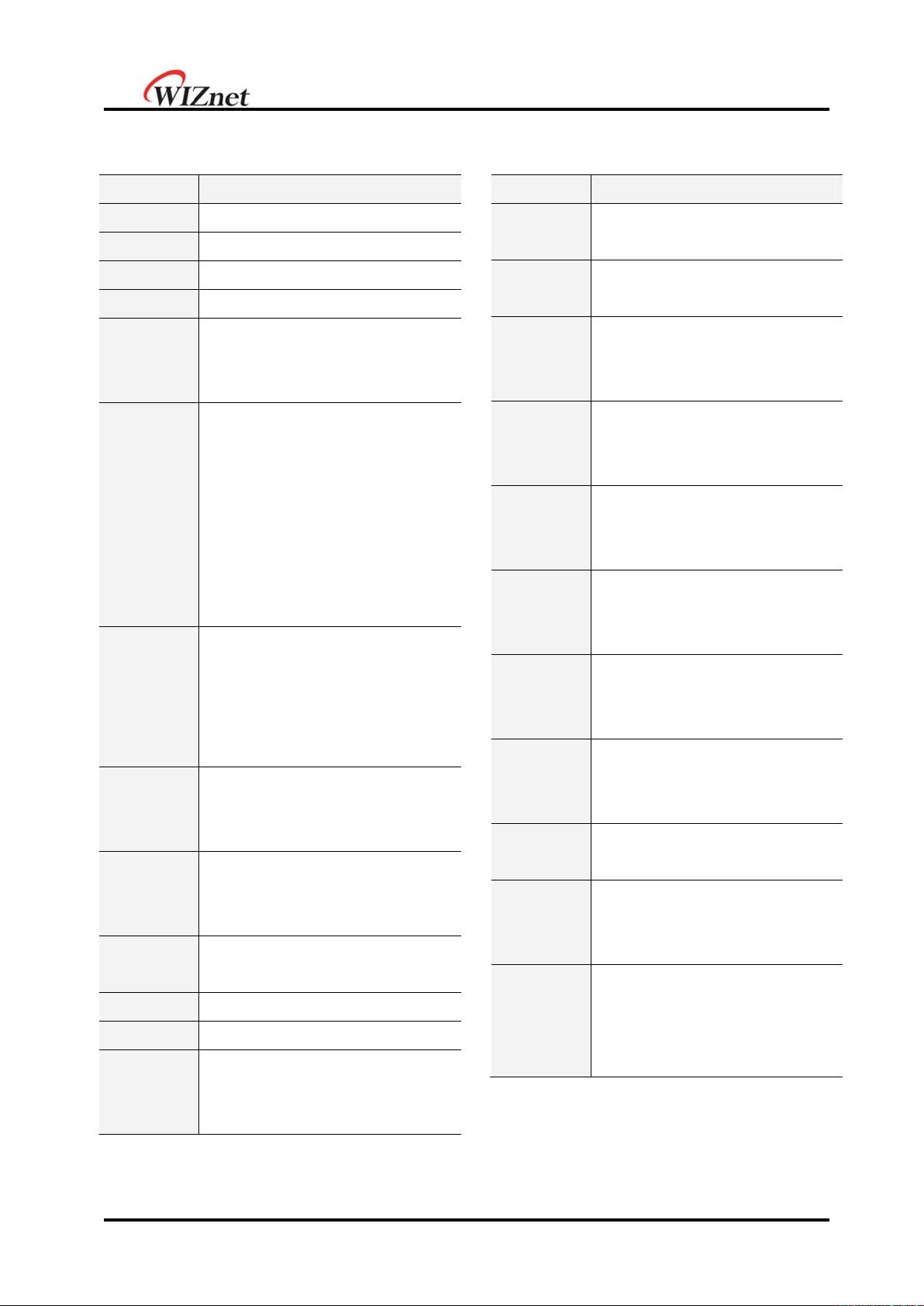

3.2 Socket registers

Note : n is socket number ( 0, 1, 2, 3, 4, 5, 6, 7 )

Address

Register

0x4n00

Socket n Mode (Sn_MR)

0x4n01

Socket n Command (Sn_CR)

0x4n02

Socket n Interrupt (Sn_IR)

0x4n03

Socket n Status (Sn_SR)

0x4n04

0x4n05

Socket n SourcePort

(SN_PORT0)

(SN_PORT1)

0x4n06

0x4n07

0x4n08

0x4n09

0x4n0A

0x4n0B

Socket n Destination Hardware

Address

(Sn_DHAR0)

(Sn_DHAR1)

(Sn_DHAR2)

(Sn_DHAR3)

(Sn_DHAR4)

(Sn_DHAR5)

0x4n0C

0x4n0D

0x4n0E

0x4n0F

Socket 0 Destination IP Address

(Sn_DIPR0)

(Sn_DIPR1)

(Sn_DIPR2)

(Sn_DIPR3)

0x4n10

0x4n11

Socket 0 Destination Port

(Sn_DPORT0)

(Sn_DPORT1)

0x4n12

0x4n13

Socket 0 Maximum Segment Size

(Sn_MSSR0)

(Sn_MSSR1)

0x4n14

Socket 0 Protocol in IP Raw mode

(Sn_PROTO)

0x4n15

Socket n IP TOS (Sn_TOS)

0x4n16

Socket n IP TTL (Sn_TTL)

0x4n17

~

0x4n1D

Reserved

Address

Register

0x4n1E

Receive Memory Size

(Sn_RXMEM_SIZE)

0x4n1F

Transmit Memory Size

(Sn_TXMEM_SIZE)

0x4n20

0x4n21

Socket 0 TX Free Size

(Sn_TX_FSR0)

(Sn_TX_FSR1)

0x4n22

0x4n23

Socket 0 TX Read Pointer

(Sn_TX_RD0)

(Sn_TX_RD1)

0x4n24

0x4n25

Socket 0 TX Write Pointer

(Sn_TX_WR0)

(Sn_TX_WR1)

0x4n26

0x4n27

Socket 0 RX Received Size

(Sn_RX_RSR0)

(Sn_RX_RSR1)

0x4n28

0x4n29

Socket 0 RX Read Pointer

(Sn_RX_RD0)

(Sn_RX_RD1)

0x4n2A

0x4n2B

Socket 0 RX Write Pointer

(Sn_RX_WR0)

(Sn_RX_WR1)

0x4n2C

Socket Interrupt Mask

(Sn_IMR)

0x4n2D

0x4n2E

Fragment Offset in IP header

(Sn_FRAG0)

(Sn_FRAG1)

0x4n30

~

0x4nFF

Reserved

© Copyright 2012 WIZnet Co., Inc. All rights reserved.

16

iEthernet

W5200

4 Register Descriptions

4.1 Common Registers

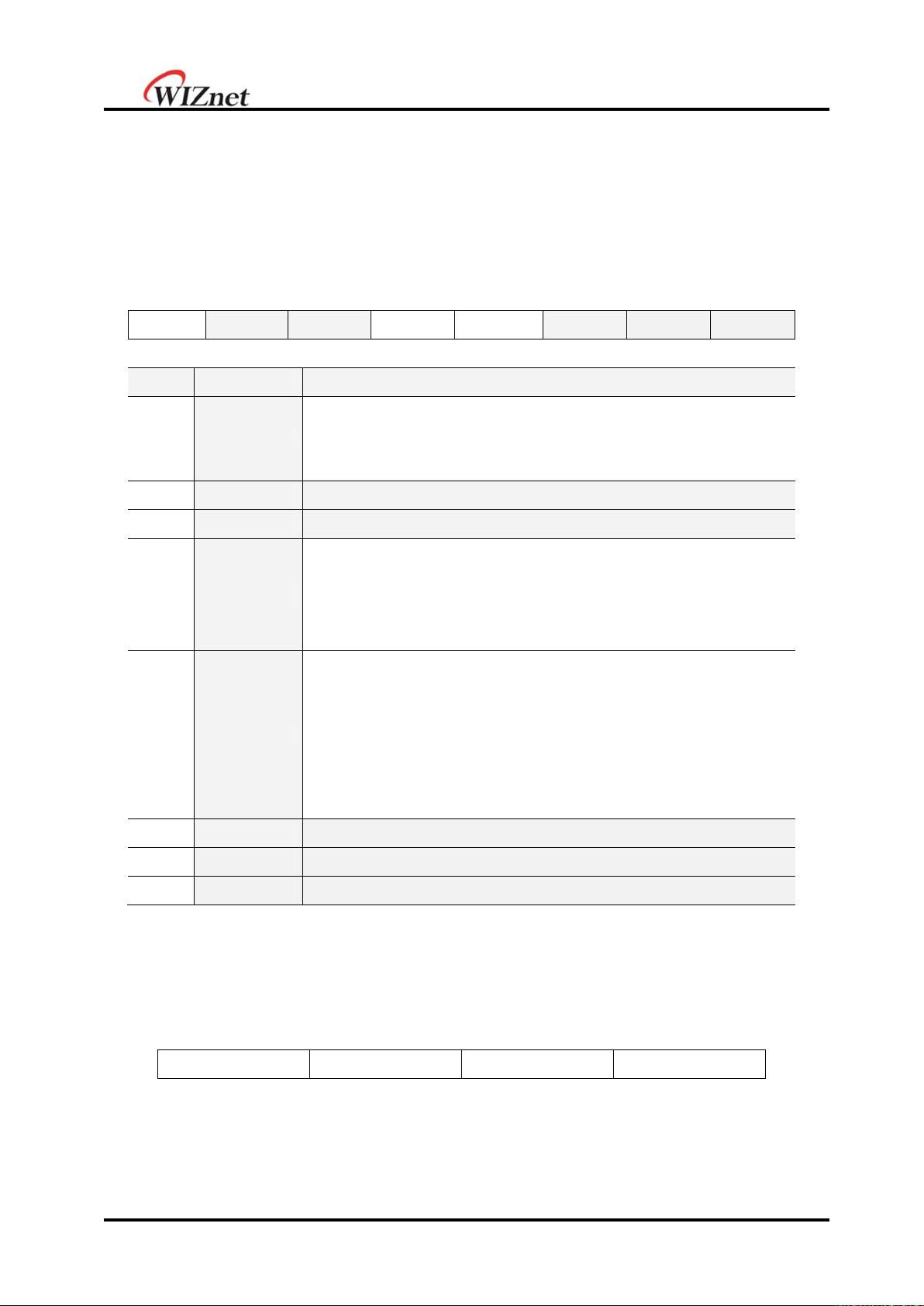

MR (Mode Register) [R/W] [0x0000] [0x00]

This register is used for S/W reset, ping block mode and PPPoE mode.

7

6

5

4

3

2

1

0

RST

PB

PPPoE

Bit

Symbol

Description

7

RST

S/W Reset

If this bit is ‘1’, internal register will be initialized. It will be

automatically cleared after reset.

6

Reserved

Reserved

5

Reserved

Reserved

4

PB

Ping Block Mode

0 : Disable Ping block

1 : Enable Ping block

If the bit is set as ‘1’, there is no response to the ping request.

3

PPPoE

PPPoE Mode

0 : DisablePPPoE mode

1 : EnablePPPoE mode

If you use ADSL without router or etc, you should set the bit as

‘1’ to connect to ADSL Server. For more detail, refer to the

application note, “How to connect ADSL”.

2

Reserved

Reserved

1

Reserved

Reserved

0

Reserved

Reserved

GAR (Gateway IP Address Register) [R/W] [0x0001 – 0x0004] [0x00]

This Register sets up the default gateway address.

Ex) In case of “192.168.0.1”

0x0001

0x0002

0x0003

0x0004

192 (0xC0)

168 (0xA8)

0 (0x00)

1 (0x01)

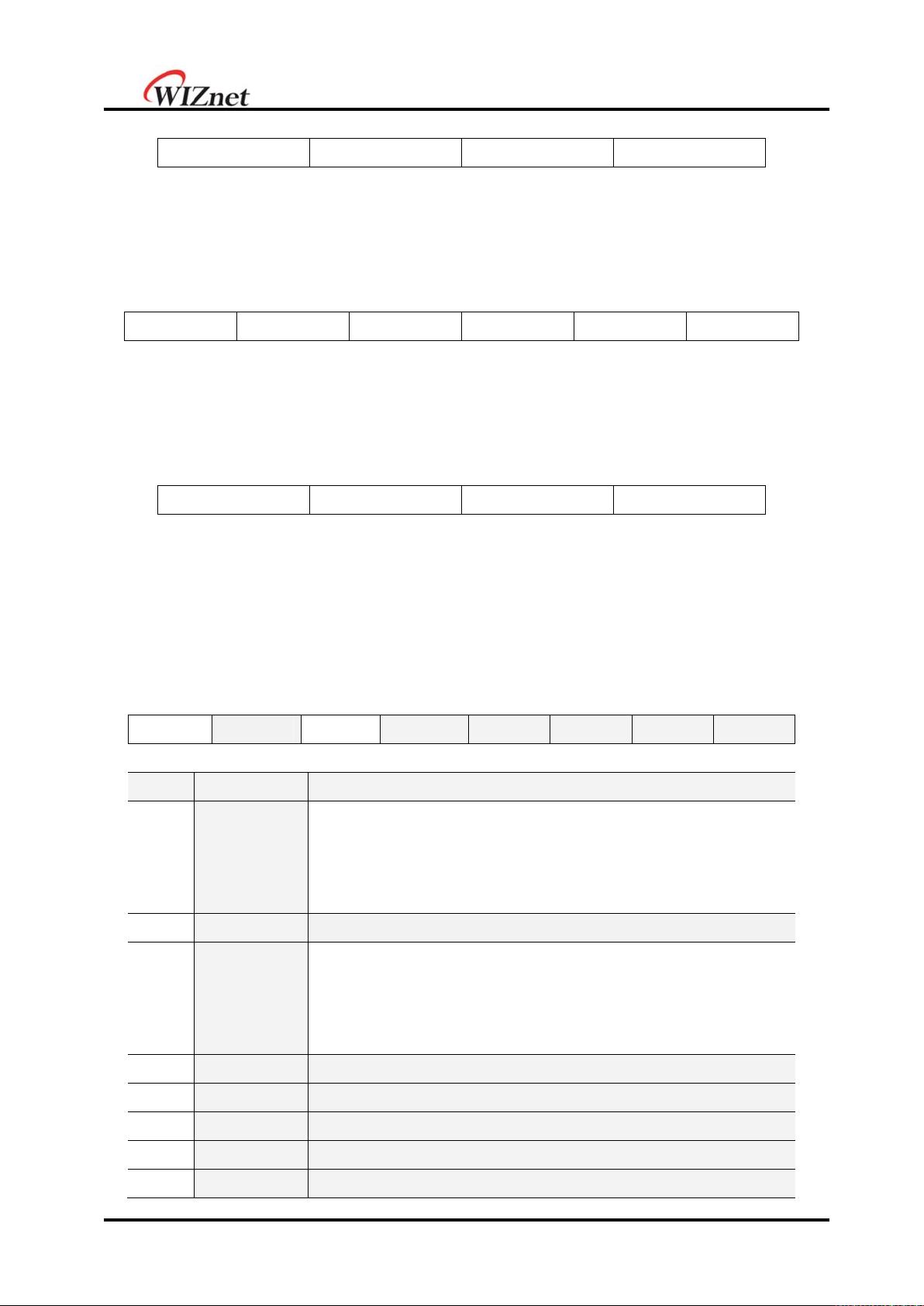

SUBR (Subnet Mask Register) [R/W] [0x0005 – 0x0008] [0x00]

This register sets up the subnet mask address.

Ex) In case of “255.255.255.0”

© Copyright 2012 WIZnet Co., Inc. All rights reserved.

17

iEthernet

W5200

0x0005

0x0006

0x0007

0x0008

255 (0xFF)

255 (0xFF)

255 (0xFF)

0 (0x00)

SHAR (Source Hardware Address Register) [R/W] [0x0009 – 0x000E] [0x00]

This register sets up the Source Hardware address.

Ex) In case of “00.08.DC.01.02.03”

0x0009

0x000A

0x000B

0x000C

0x000D

0x000E

0x00

0x08

0xDC

0x01

0x02

0x03

SIPR (Source IP Address Register) [R/W] [0x000F – 0x0012] [0x00]

This register sets up the Source IP address.

Ex) In case of “192.168.0.2”

0x000F

0x0010

0x0011

0x0012

192 (0xC0)

168 (0xA8)

0 (0x00)

2 (0x02)

IR (Interrupt Register) [R] [0x0015] [0x00]

This register is accessed by the host processor to know the cause of interrupt. Any

interruption can be masked in the Interrupt Mask Register (IMR). The nINT signal retain low

as long as any masked signal is set, and will not go high until all masked bits in this Register

have been cleared.

7

6

5

4

3

2

1

0

CONFLICT

Reserved

PPPoE

Reserved

Reserved

Reserved

Reserved

Reserved

Bit

Symbol

Description

7

CONFLICT

IP Conflict

It is set as ‘1’ when there is ARP request with same IP address

as Source IP address. This bit is cleared to ‘0’ by writing ‘1’ to

this bit.

6

Reserved

Reserved

5

PPPoE

PPPoE Connection Close

In the Point-to-Point Protocol over Ethernet (PPPoE) Mode, if

the PPPoE connection is closed, ‘1’ is set. This bit will be

cleared to ‘0’ by writing ‘1’ to this bit.

4

Reserved

Reserved

3

Reserved

Reserved

2

Reserved

Reserved

1

Reserved

Reserved

0

Reserved

Reserved

剩余84页未读,继续阅读

xiaowei2014

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 最优条件下三次B样条小波边缘检测算子研究

- 深入解析:wav文件格式结构

- JIRA系统配置指南:代理与SSL设置

- 入门必备:电阻电容识别全解析

- U盘制作启动盘:详细教程解决无光驱装系统难题

- Eclipse快捷键大全:提升开发效率的必备秘籍

- C++ Primer Plus中文版:深入学习C++编程必备

- Eclipse常用快捷键汇总与操作指南

- JavaScript作用域解析与面向对象基础

- 软通动力Java笔试题解析

- 自定义标签配置与使用指南

- Android Intent深度解析:组件通信与广播机制

- 增强MyEclipse代码提示功能设置教程

- x86下VMware环境中Openwrt编译与LuCI集成指南

- S3C2440A嵌入式终端电源管理系统设计探讨

- Intel DTCP-IP技术在数字家庭中的内容保护

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功