NXP Semiconductors

MPL3115A2

MPL3115A2

10 / 52

SCL

SDA

10.1 I

2

C characteristics

I

2

CSymbol Parameter

f

SCL

0 400 kHz

f

SCL

0 4 MHz

t

BUF

— 1.3 — µs

t

HD;STA

— 0.6 — µs

t

SU;STA

— 0.6 — µs

t

SU;STO

— 0.6 — µs

t

HD;DAT

— 50 —

t

SU;DAT

— 100 —

t

LOW

— 1.3 — µs

t

HIGH

— 0.6 — µs

— 20 + 0.1C

b

300

t

f

— 20+ 0.1C

b

300

t

SP

— — 50

[1]

[2]

[3]

[4]

[5]

[6]

[7]

带高度计的I2C精密压力传感器

本文档中提供的所有信息均受法律免责声明的约束。

NXPB.V.2018。保留所有权利。

数据表:技术数据 修订版7—2018年2月15日

10数字接口

通过I2C串行接口访问嵌入在设备中的寄存器。

表7.串行接口引脚说明

姓名 描述

I2C串行时钟

I2C串行数据

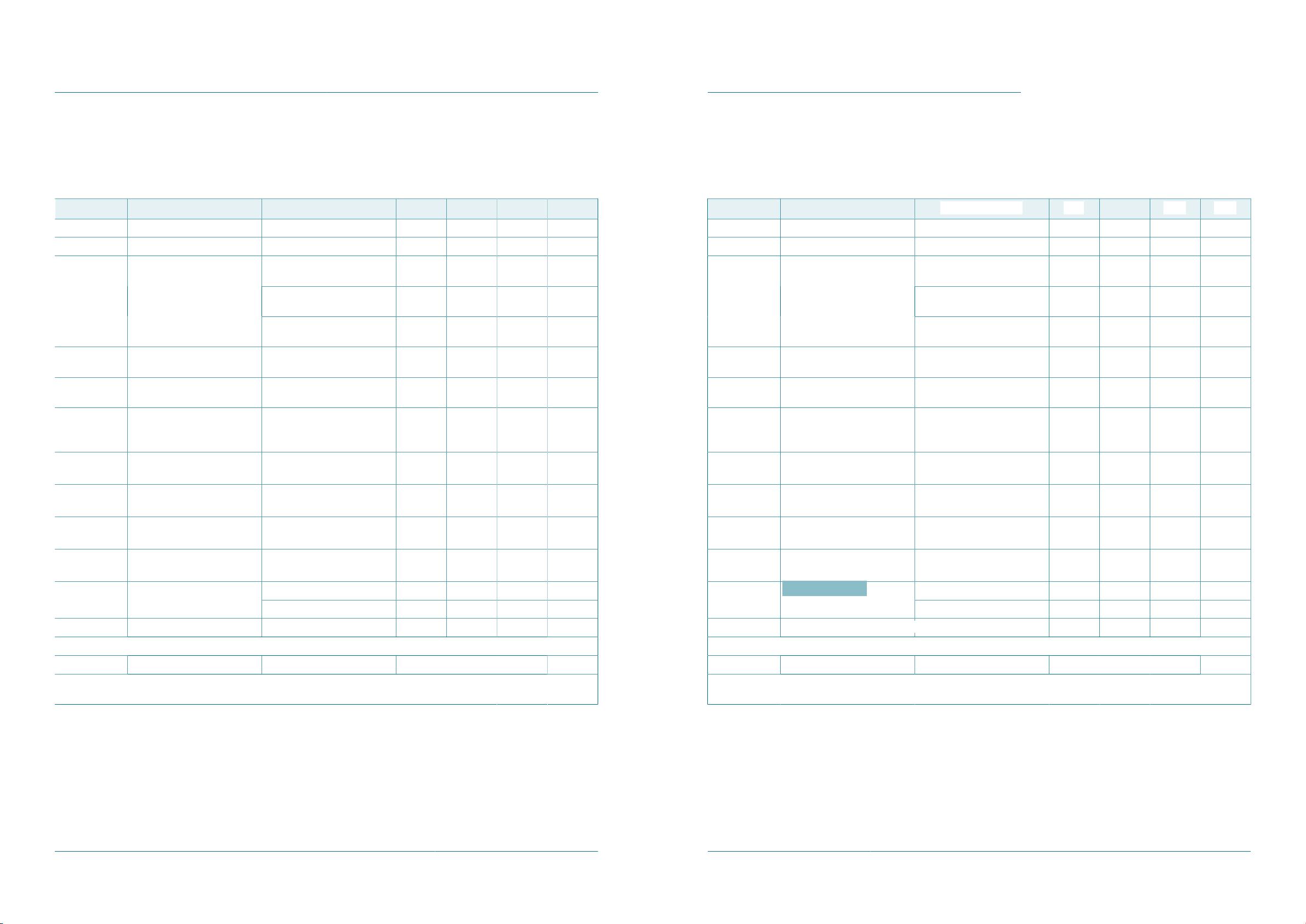

表8.I2C从器件时序值所有值均参考VIH(min)和VIL(

max)电平。

健康)状况

最小

最大限

度

单元

SCL时钟频率 上拉=1kΩ,Cb=400pF

SCL时钟频率 上拉=1kΩ,Cb=20pF

STOP和START条件之间的总

线空闲时间

重复START保持时间

重复START设置时间

STOP条件建立时间

SDA数据保持时间[1][2][3]

纳秒

SDA建立时间[4]

纳秒

SCL时钟低电平时间

SCL时钟高电平时间

tr

SDA和SCL上升时间[5]

纳秒

SDA和SCL下降时间[2][5][6][7]

纳秒

内部输入滤波器抑制的尖峰

脉冲宽度

纳秒

器件必须在内部为SDA信号(相对于SCL信号的VIH(min))提供至少300ns的保持时间,以桥接SCL下降沿的未定义区域

最大tHD;DAT必须比tVD;DAT或tVD;ACK的最大值小一个转换时间。该器件不会延长SCL信号的低电平周期(tLOW)。

快速模式I2C设备可用于标准模式I2C系统,但必须满足tSU;DAT250ns的要求。如果器件不延长SCL信号的低电平周期,

就会自动出现这种情况。如果这样的设备确实延长了SCL信号的LOW周期,则它必须在之前将下一个数据位输出到SDA

线tr(max)+tSU;DAT=1000+250=1250ns(根据标准模式I2C规范)SCL线被释放。此外,确认时序必须满足此建立时间。

Cb=以pF为单位的一条总线线路的总电容。

SDA和SCL总线的最大tf指定为300ns。SDA输出级tf的最大下降时间规定为250ns。这允许串联保护电阻连接在SDA和S

CL引脚以及SDA/SCL总线之间,而不会超过指定的最大tf。

在快速模式plus中,输出级和总线时序的下降时间指定相同。如果使用串联电阻,设计人员在考虑总线时序时应考虑到这一点。

趣卡社区(www.qukaa.com)

NXP Semiconductors

MPL3115A2

I

2

C precision pressure sensor with altimetry

MPL3115A2 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserved.

Data sheet: technical data Rev. 7 — 15 February 2018

10 / 52

10 Digital interface

The registers embedded inside the device are accessed through an I

2

C serial interface.

Table 7. Serial interface pin descriptions

Name Description

SCL I

2

C serial clock

SDA I

2

C serial data

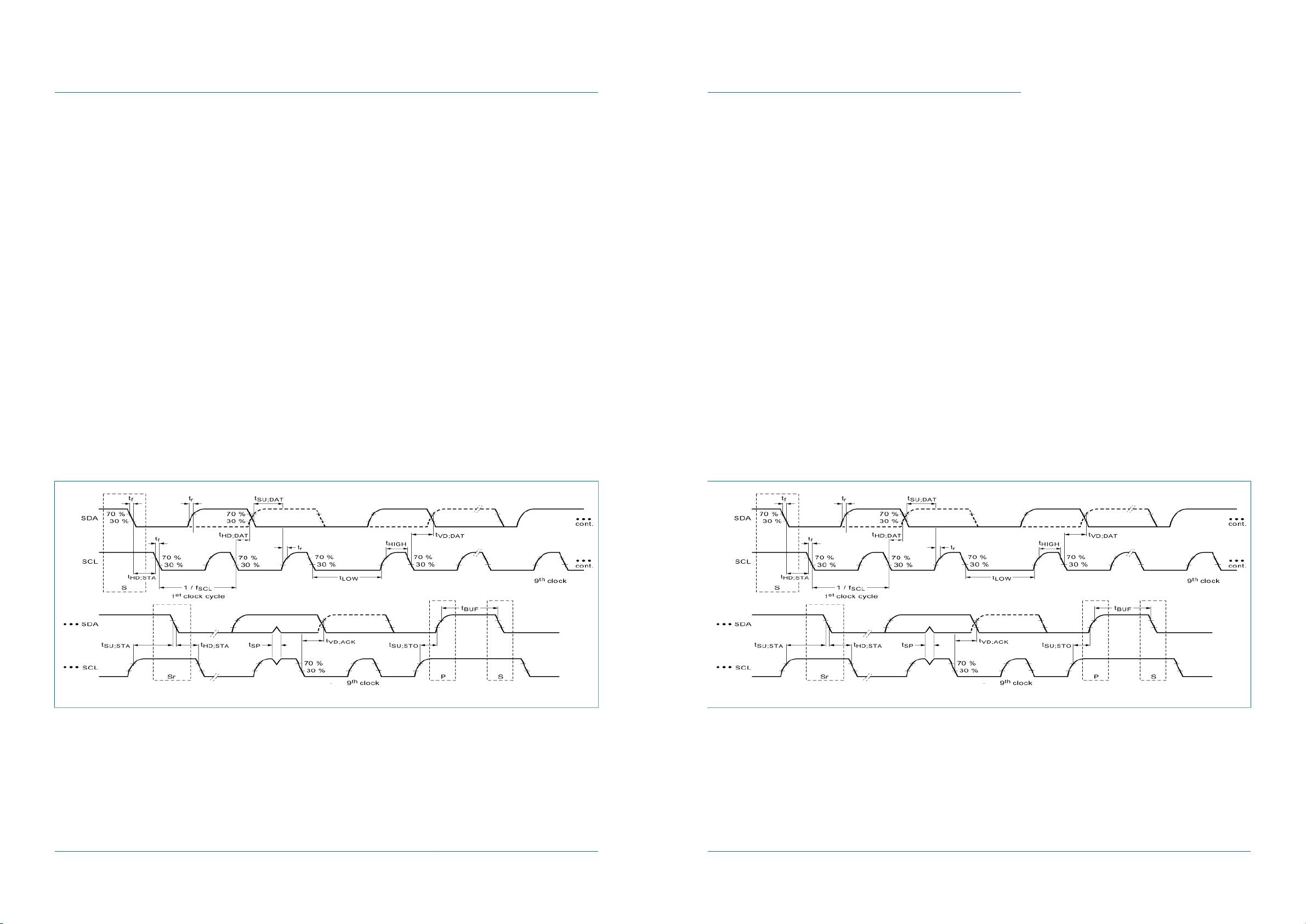

10.1 I

2

C characteristics

Table 8. I

2

C Slave timing values

All values referred to VIH(min) and VIL(max) levels.

I

2

CSymbol Parameter

Condition Min Max

Unit

f

SCL

SCL clock frequency Pull-up = 1 kΩ, Cb = 400 pF 0 400 kHz

f

SCL

SCL clock frequency Pull-up = 1 kΩ, Cb = 20 pF 0 4 MHz

t

BUF

Bus free time between STOP

and START condition

— 1.3 — µs

t

HD;STA

Repeated START hold time — 0.6 — µs

t

SU;STA

Repeated START setup time — 0.6 — µs

t

SU;STO

STOP condition setup time — 0.6 — µs

t

HD;DAT

SDA data hold time

[1][2][3]

— 50 — ns

t

SU;DAT

SDA setup time

[4]

— 100 — ns

t

LOW

SCL clock low time — 1.3 — µs

t

HIGH

SCL clock high time — 0.6 — µs

t

r

SDA and SCL rise time

[5]

— 20 + 0.1C

b

300 ns

t

f

SDA and SCL fall Time

[2][5][6][7]

— 20+ 0.1C

b

300 ns

t

SP

Pulse width of spikes that are

suppressed by internal input

filter

— — 50 ns

[1] t

HD;DAT

is the data hold time that is measured from the falling edge of SCL, applies to data in transmission and the acknowledge.

[2] The device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the VIH(min) of the SCL signal) to bridge the

undefined region of the falling edge of SCL

[3] The maximum t

HD;DAT

must be less than the maximum of t

VD;DAT

or t

VD;ACK

by a transition time. This device does not stretch the LOW period (t

LOW

) of the

SCL signal.

[4] A fast mode I

2

C device can be used in a standard mode I

2

C system, but the requirement t

SU;DAT

250 ns must then be met. This will automatically be the

case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the

next data bit to the SDA line t

r

(max) + t

SU;DAT

= 1000 + 250 = 1250 ns (according to the standard mode I

2

C specification) before the SCL line is released.

Also the acknowledge timing must meet this set-up time.

[5] Cb = Total capacitance of one bus line in pF.

[6] The maximum t

f

for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t

f

is specified at 250 ns. This

allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum

specified t

f

.

[7] In fast mode plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when

considering bus timing.