Quartus设计流程中的NetlistViewer:RTL与Technology Map分析

需积分: 33 180 浏览量

更新于2024-07-19

1

收藏 4.28MB PDF 举报

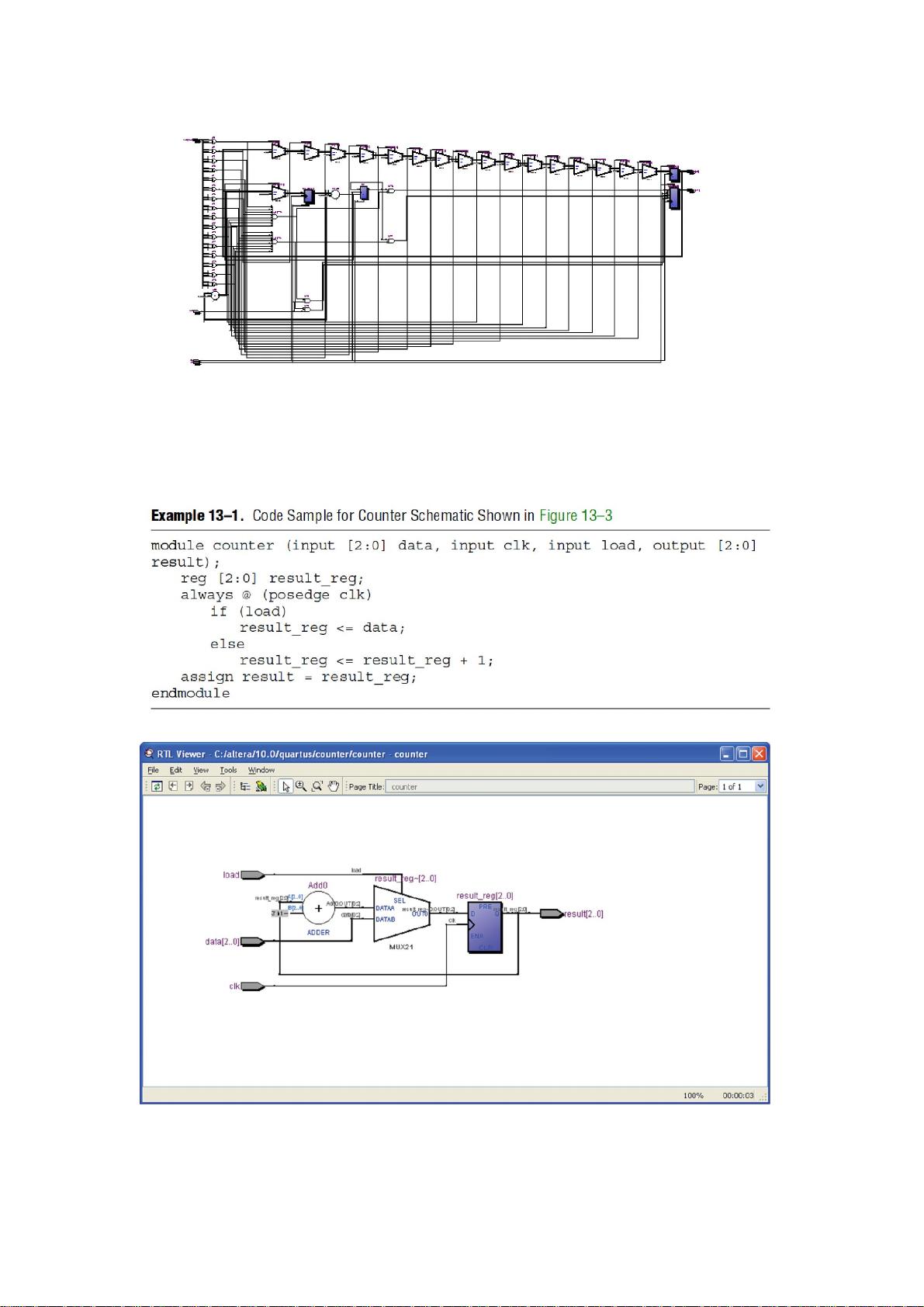

"这篇文档介绍了网表查看器(Netlist Viewer)的相关知识,特别是其在电子设计自动化(EEDA)中的应用,包括RTL Viewer、StateMachine Viewer和Technology Map Viewer。该工具主要用于查看和理解设计的高层次表示以及经过映射后的技术实现。"

在电子设计领域,网表查看器是不可或缺的工具,它帮助设计师理解和分析设计的不同阶段。以下是关于这个工具的详细信息:

1. **符号(Symbols)**:在网表查看器中,符号是电路设计的基本元素,代表了逻辑门、触发器等基本电路单元。它们提供了一个直观的方式来查看和理解设计的组成。

2. **视图(View)**:视图选项允许用户选择不同的展示方式,例如RTL视图、状态机视图和映射后技术视图,每种视图都对应设计的不同阶段和抽象级别。

3. **导航Schematic View**:

- **原子原语内容的查看**:原子原语是设计中最基本的单元,用户可以通过工具查看其内部细节。

- **LUT表示在Technology Map Viewer中的查看**:逻辑单元阵列(LUT)是FPGA中的基础资源,用于实现逻辑功能。Technology Map Viewer显示这些LUT如何映射到实际硬件。

- **组合逻辑分组为Logic Clouds**:为了简化复杂设计,组合逻辑常被组织成逻辑云,便于理解。

- **跨页面跟踪网络(Nets)**:设计可能分布在多个页面上,工具支持追踪网络在整个设计中的连接。

4. **过滤Schematic View**:

- **类型(Types)**:用户可以根据特定类型的元件或连接进行过滤,以便更专注于设计的特定部分。

- **跨层次过滤**:在层次化设计中,可以过滤不同层次的信息,突出显示特定层次的内容。

5. **查看时序路径**:在优化阶段,查看时序路径有助于理解设计的性能瓶颈,并进行必要的时序分析和优化。

6. **Netlist Viewer的种类**:

- **RTL Viewer**:RTL(寄存器传输级)查看器展示了未经过优化的设计,接近于源代码级别的表示,有利于理解设计意图。

- **StateMachine Viewer**:主要用于查看状态机的设计,简洁明了地呈现状态转换和控制逻辑。

- **Technology Map Viewer**:在映射之后,此查看器显示了如何将设计映射到具体FPGA器件的逻辑资源,包括LUT、触发器等。

在Quartus设计流程中,不同的Netlist Viewer在不同的设计阶段有着不同的用途。例如,RTL Viewer用于前综合分析,而Technology Map Viewer则用于后综合的硬件映射分析。由于Netlist Viewer显示的是最近一次成功编译的结果,所以在出现错误后,必须重新编译以获取更新的视图。

Netlist Viewer是设计验证和调试的关键工具,通过它,设计师可以深入理解设计的内部工作原理,优化逻辑,确保设计符合预期的性能和功能。无论是对于初学者还是经验丰富的工程师,掌握网表查看器的使用都是提高设计效率的重要步骤。

点击了解资源详情

点击了解资源详情

点击了解资源详情

1566 浏览量

1216 浏览量

762 浏览量

jack_arm

- 粉丝: 3

- 资源: 10

最新资源

- 逻辑分析仪使用手册特备版

- C语言测试-想成为嵌入式程序员应知道的0x10个基本问题.doc

- ASP考试系统理论指导

- PSoC的动态配置能力及其实现方法

- java面试题集(100题)

- 马潮老师AVR新书《AVR单片机嵌入式系统原理与应用实践》.

- 程序员面试好东西 JAVA

- AIX 逻辑卷管理

- 在Linux世界驰骋系列之Shell编程

- 直流电源及数显电路的设计

- OSWorkflow中文手册.pdf

- OSWorkflow开发指南.pdf

- Webwork2 开发指南.pdf

- Bootloader+Source+Code+Modification+Guide.pdf

- Hibernate开发指南.pdf

- 华为编程规范——规范你的程序设计