高速电路设计:信号完整性的关键挑战与解决方案

需积分: 9 55 浏览量

更新于2024-09-18

收藏 366KB DOCX 举报

"高速电路设计中信号完整性分析"

在高速电路设计中,信号完整性(Signal Integrity, SI)分析是一项至关重要的任务,特别是在当前电子设备时钟频率和上升时间不断提升的背景下。传统的低速逻辑设计中,信号完整性问题并不突出,但随着技术的发展,这些问题已经成为影响系统性能的关键因素。

信号完整性主要涉及以下几个核心概念:

1. 特征阻抗控制:特征阻抗是信号在传输线上传输时所呈现的等效电阻,它决定了信号的能量损耗和反射。保持信号路径的特征阻抗一致是减少反射和保持信号质量的关键。在PCB设计中,设计师需要计算并选择合适的线宽、间距和介质厚度,以确保信号线的特征阻抗与连接的元件阻抗匹配。

2. 终端匹配:终端匹配是为了消除信号在传输线末端的反射,通常通过添加匹配网络(如串联电阻或并联电容)来实现。匹配良好的终端能减少信号反射,提高信号质量,防止信号失真和抖动。

3. 电源和地平面:电源和地平面是高速电路的“骨架”,提供稳定的电压参考和电流回路。良好的电源和地平面布局可以减少噪声耦合,提高信号完整性。通常采用分割电源层和地平面的方法,以减少不同部分电路间的干扰。

4. 信号布线和串扰:信号线的布局直接影响串扰,即一个信号线对周围信号线产生的电磁影响。合理规划信号路径,避免紧密平行和长直段,可以减少串扰。使用屏蔽、分割平面或增加间距等手段也能有效抑制串扰。

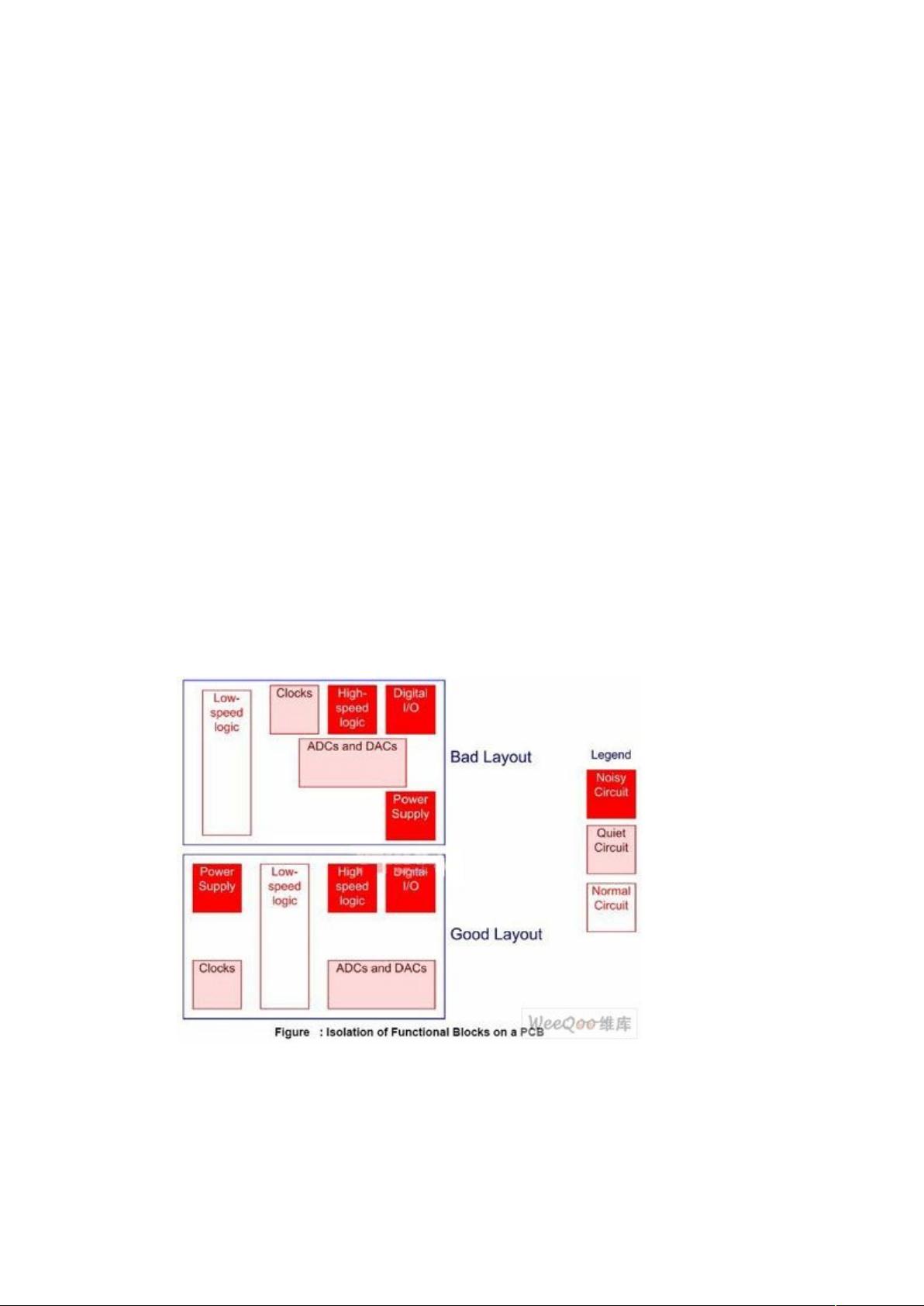

5. 噪声管理:高速电路中的噪声源包括电源噪声、开关噪声、辐射噪声等。设计时应考虑噪声源的位置和强度,通过隔离、滤波和屏蔽等手段降低噪声对信号完整性的影响。

6. 高速IC接口设计:高速IC接口如DDR、PCIe等,需要考虑接口的信号完整性,如眼图分析、时序裕量等,以确保数据传输的准确性和可靠性。

7. SI仿真工具:利用仿真软件(如HyperLynx、ADS等)进行信号完整性分析,可以帮助设计师在设计早期发现潜在问题,优化设计,避免在后期修改造成的时间和成本浪费。

高速电路设计中的信号完整性分析是一个综合考虑多个因素的过程,包括元件选择、PCB布局、布线策略以及噪声控制等。理解并掌握这些概念和技术,对于提升电路的性能和可靠性至关重要。设计师应当在设计初期就充分考虑信号完整性,以实现高效、可靠的高速系统。

190 浏览量

点击了解资源详情

点击了解资源详情

196 浏览量

2023-11-17 上传

105 浏览量

2020-08-27 上传

227 浏览量

Jackey_xiao

- 粉丝: 1

- 资源: 5