Verilog HDL实现的数字频率计设计

版权申诉

"基于Verilog HDL的数字频率计设计文档"

在电子测量技术领域,频率测量是一项基础且至关重要的任务。数字频率计是一种用于测量信号频率的设备,它能够准确地计算出输入信号在一个特定时间间隔内产生的脉冲数量。在实际应用中,频率测量广泛应用于诸如力的测量(振弦式方法)、时间测量、速度控制等多种场景,这些都可以通过转换为频率测量来实现。

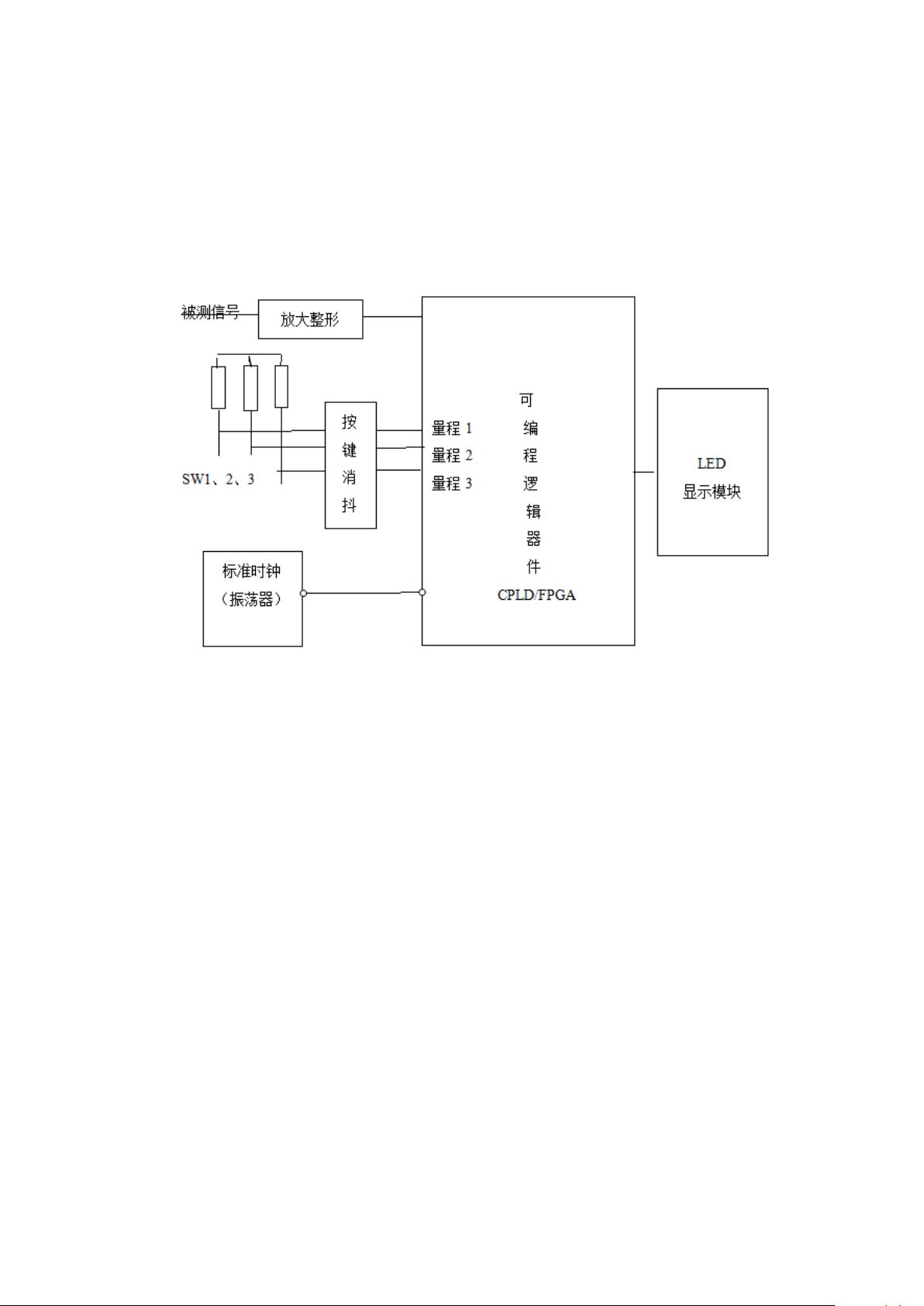

本设计文档详细介绍了如何使用Verilog HDL(硬件描述语言)来设计一个基于CPLD(复杂可编程逻辑器件)的简易数字频率计。Verilog HDL是一种强大的工具,它允许工程师以类似于编程的语言来描述数字系统的硬件行为,从而实现电路设计的抽象和模块化。

设计的频率计涵盖了10Hz到100MHz的宽频率范围,具备自适应量程调整功能,可以根据输入信号的频率自动选择合适的测量模式。其工作原理主要包括两个主要部分:一是分频计数器,它将输入的高频信号分频,使其频率降低到可以由计数器处理的范围;二是计数器,它在设定的闸门时间内统计分频后的脉冲个数,从而计算出原始信号的频率。

直接测频法是适用于高频信号的测量方法,通过测量一定时间内的脉冲数来计算频率;而间接测频法,如周期测频法,则适用于低频信号,通过测量信号的周期来确定频率。在这个设计中,Verilog HDL语言的灵活性使得这两种方法可以灵活结合,以适应不同的测量需求。

频率计的输出是BCD码(二进制编码的十进制数)形式,可以直接驱动七段LED显示器,直观地显示出测量结果。这样的设计不仅提高了测量的准确性,也简化了用户界面,使得操作更为简便。此外,由于采用了CPLD器件,整个系统具有小型化、高可靠性和低功耗的优点,适合于各种现场或实验室环境的应用。

关键词:数字频率计、Verilog HDL、分频计数器、电子计数器、直接测频法、间接测频法、CPLD、闸门时间、BCD码、七段LED显示。

该文档提供了一个实用的参考案例,展示了如何利用现代电子设计技术和Verilog HDL语言,开发一个功能全面、性能优异的数字频率计,对于学习者和电子工程师来说,具有很高的实践价值。

158 浏览量

208 浏览量

129 浏览量

2022-06-21 上传

2023-06-20 上传

146 浏览量

133 浏览量

124 浏览量

老帽爬新坡

- 粉丝: 99

最新资源

- CS555第五团队项目Java实战演练

- VC宝典源代码解析与实践指南

- 深度解析AlexNet网络模型及其训练过程

- 4GTRX-KIT-SW V6.0.0.3固件更新及功能介绍

- 迈乐安卓电视盒SD卡刷机教程与工具

- Android 5.0 Camera与Camera2源码分析

- Android滚动字幕跑马灯效果Demo演示及库文件分享

- 掌握公钥加密:RSA算法的详细实现与库应用

- 离子液体钙盐的CalculadoraSalario:TypeScript实现

- JLink V5.12驱动程序下载与安装指南

- 在Delphi7中使用fastreport2.5打印二维码的方法

- 芯片时序分析方法与多芯片操作指南

- PHP中文目录操作类:实现文件夹与文件管理功能

- 基于混合特征选择的建筑能耗预测新方法

- 解决Mac下Hadoop2.8.1无法加载本地库的教程

- 易语言实现高效Mysql用户管理增删改查操作