Verilog HDL数字频率计设计详解与实现

版权申诉

本课程设计文档是关于"基于Verilog HDL数字频率计设计与实现"的项目,针对的是计算机与通信工程学院网络工程专业的学生,作为计算机组成原理课程的一部分,于2010~2011学年第一学期第17~18周进行。课程的主要目标是让学生通过实践学习和掌握计算机组成原理的分析与设计方法,提升他们的实际操作技能。

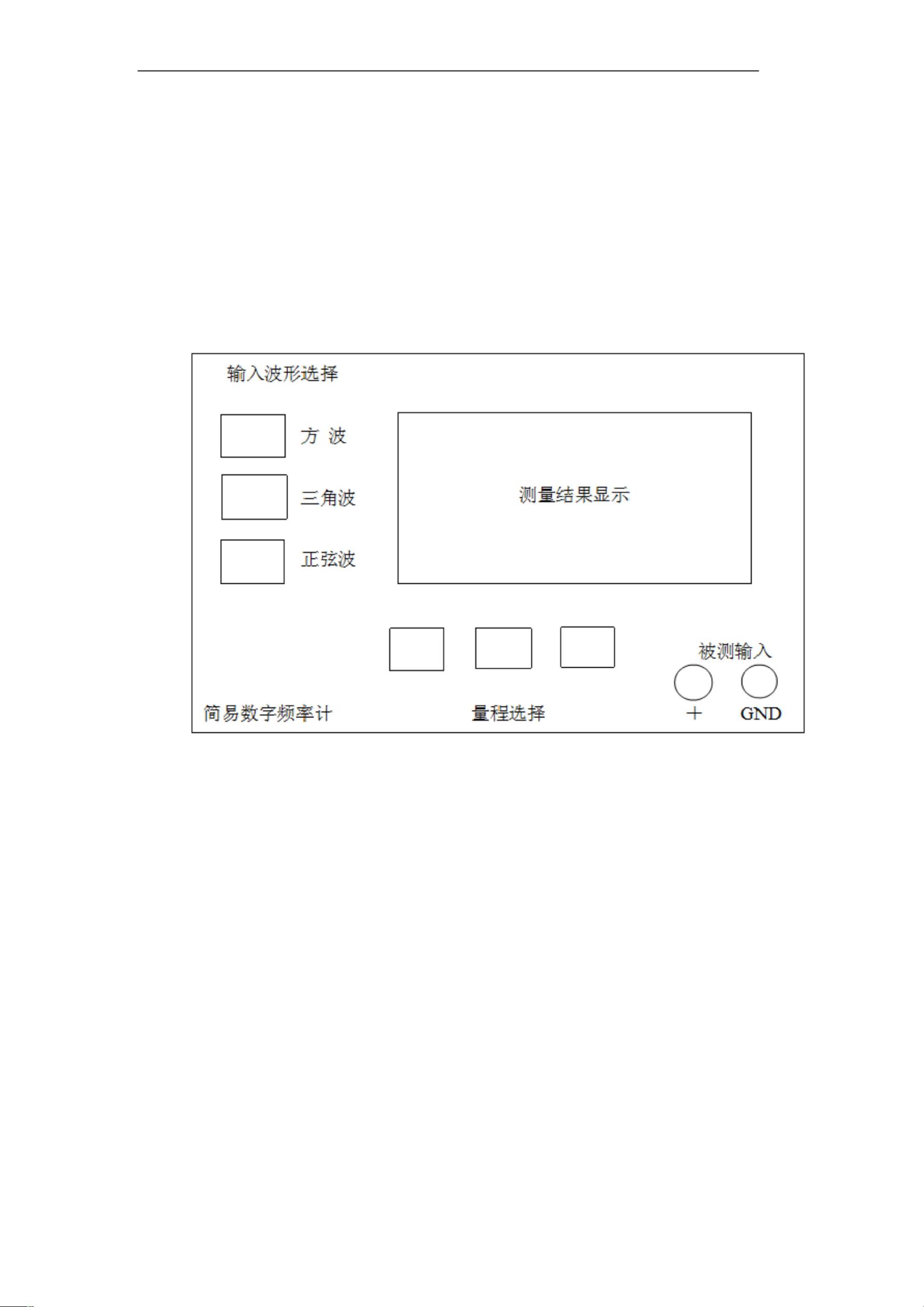

课题的核心是设计一个数字频率计,它在电子技术中具有重要意义,因为频率测量对于许多电路性能评估和信号处理至关重要。电子计数器作为一种常用的测频工具,其直接测频法适用于高频信号,而间接测频法则适用于低频信号。本文将利用Verilog HDL,一种高级硬件描述语言,来实现这一设计。

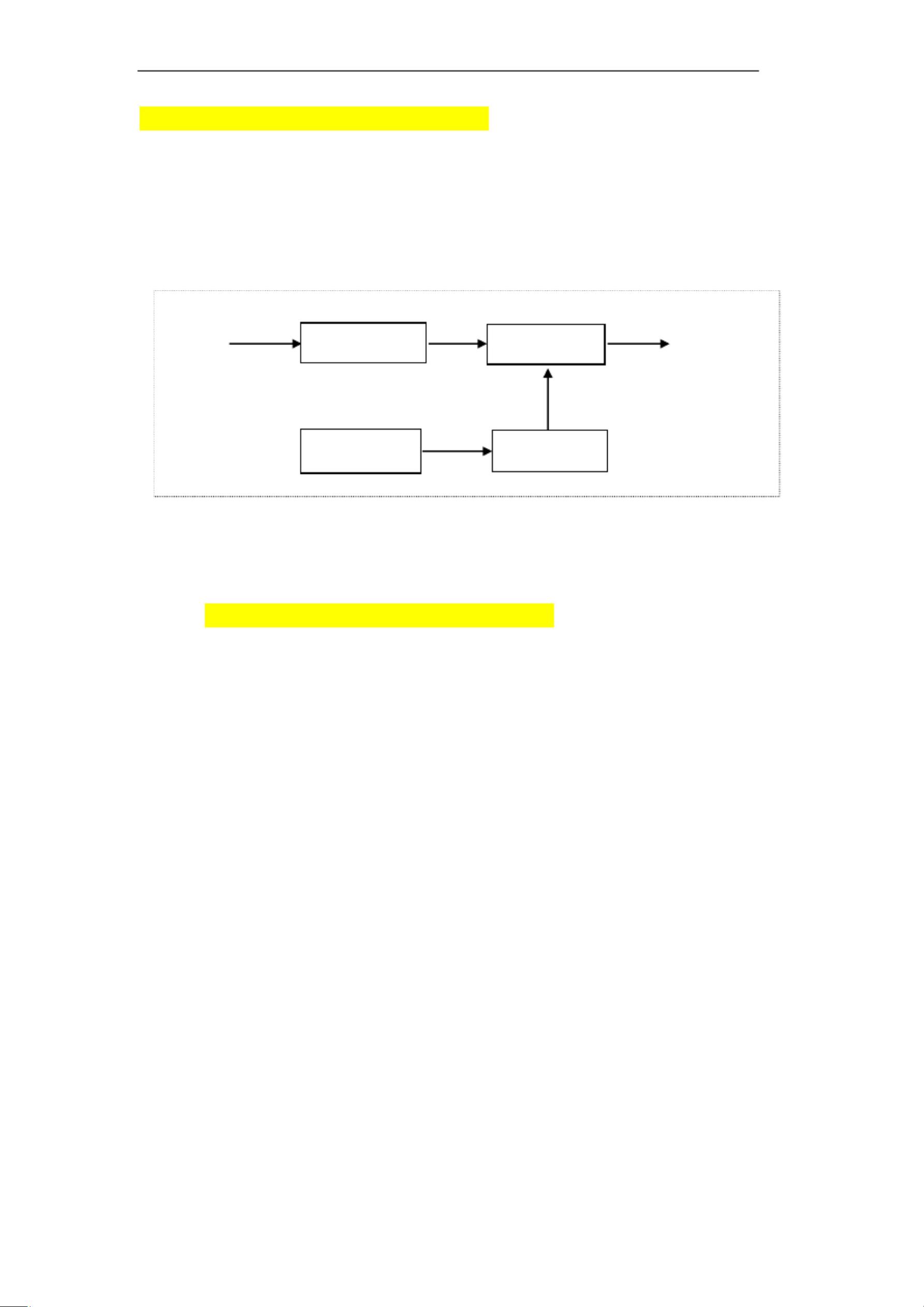

Verilog HDL部分,作为一门用于描述数字系统行为的语言,它的简介被纳入课程内容,强调其简洁明了的语法和强大的系统级描述能力。课程设计的系统框图被详细地展示出来,包括计数模块、门控模块、分频模块、寄存器模块、多路选择模块以及动态位选模块和BCD译码模块等关键组成部分。

设计过程中,学生需根据系统的模块划分结构进行编程,每个模块都对应着特定的功能,如计数模块负责脉冲计数,门控模块控制信号流程,分频模块进行频率转换,寄存器模块存储数据,多路选择模块则用于选择信号路径,而动态位选模块和BCD译码模块则确保数据显示的准确性和可读性。

此外,该课程设计还强调了文献收集与分析的重要性,学生需对当前频率计测量的相关技术进行研究,分析其现状,并在课程设计报告书中清晰地阐述设计思路、实现过程和实验结果。课程设计的最终评价不仅包括学生的代码质量,还包括他们撰写论文的能力以及设计过程中体现的严谨态度。

总结起来,本课程设计旨在通过实践应用Verilog HDL,使学生深入理解计算机组成原理并掌握硬件设计技能,同时培养他们独立解决问题和撰写技术报告的能力。通过这个项目,他们将能够开发出一个可实际使用的数字频率计,并对其工作原理有深刻的理解。

148 浏览量

124 浏览量

148 浏览量

2022-01-11 上传

2023-10-18 上传

2022-10-14 上传

257 浏览量

2022-06-16 上传

苦茶子12138

- 粉丝: 1w+

- 资源: 7万+

最新资源

- DQLab-Machine-Learning-With-Python-for-Beginner:初学者使用Python进行机器学习

- SRename拖把更名.rar

- compose-challenge-3

- 商业编程-源码-随缘网络PHP留言板(带审核功能) v1.0 build 091017.zip

- scipipe:使用Go和命令行的健壮,灵活且资源高效的管道

- 新箭 JS14A系列电子式时间继电器使用说明书.rar

- install_name_tool:苹果的install_name_toolLinux端口

- tetrapy:俄罗斯方块在Python中的克隆

- scratchlink2021.zip

- MySQL:与MySQL数据库交互SQL命令

- myBeatMaker

- codepiano.github.com, 个人博客,powered by jekyll && bootstrap.zip

- Star-Review:仅使用Vanilla Javascript进行星级审查

- gotags:兼容ctags的Go标记生成器

- ChronoHelper:Unity Editor插件,允许在PlayMode中控制Time.timeScale

- 知识产权实践