JEDEC Standard No. 230B

Page 5

2.6 Pin description

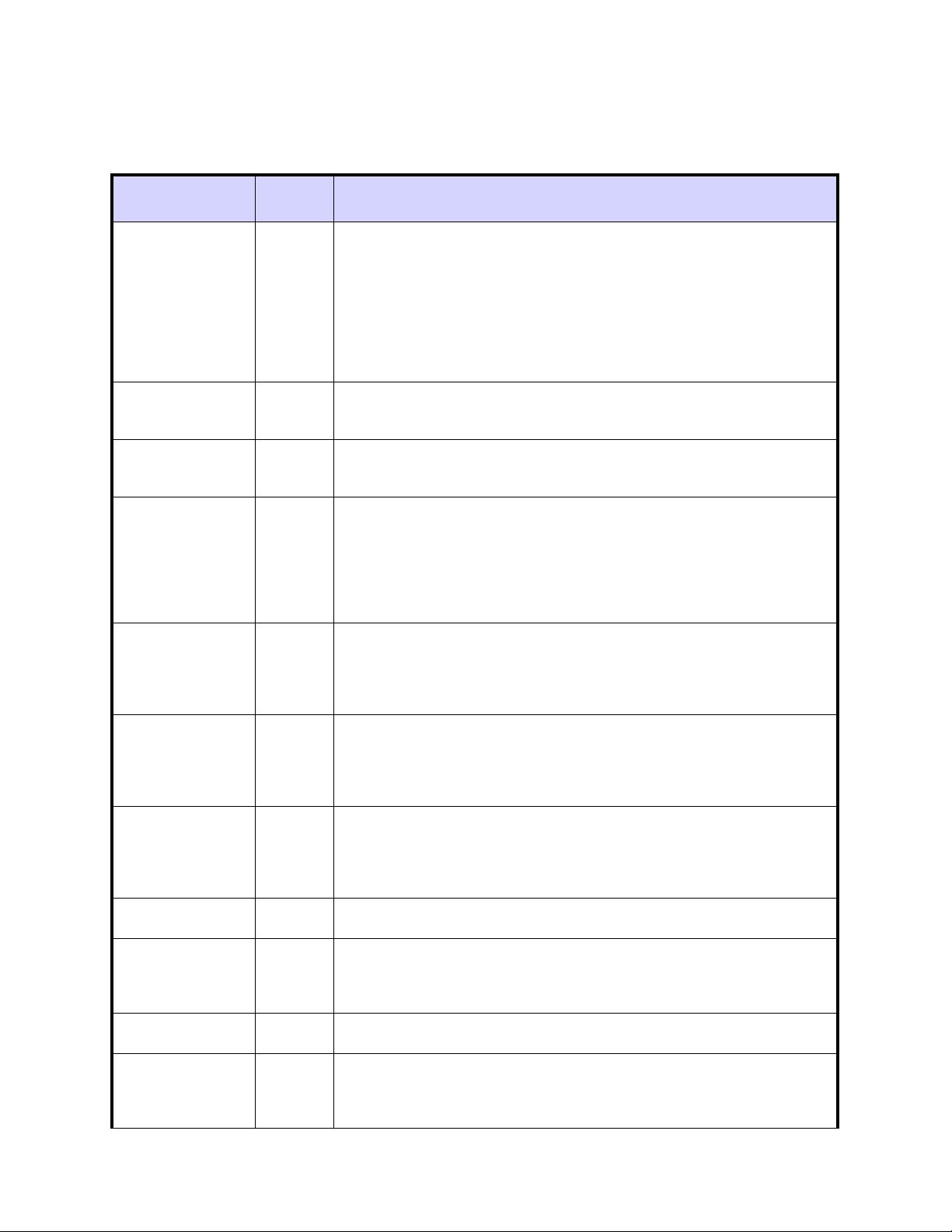

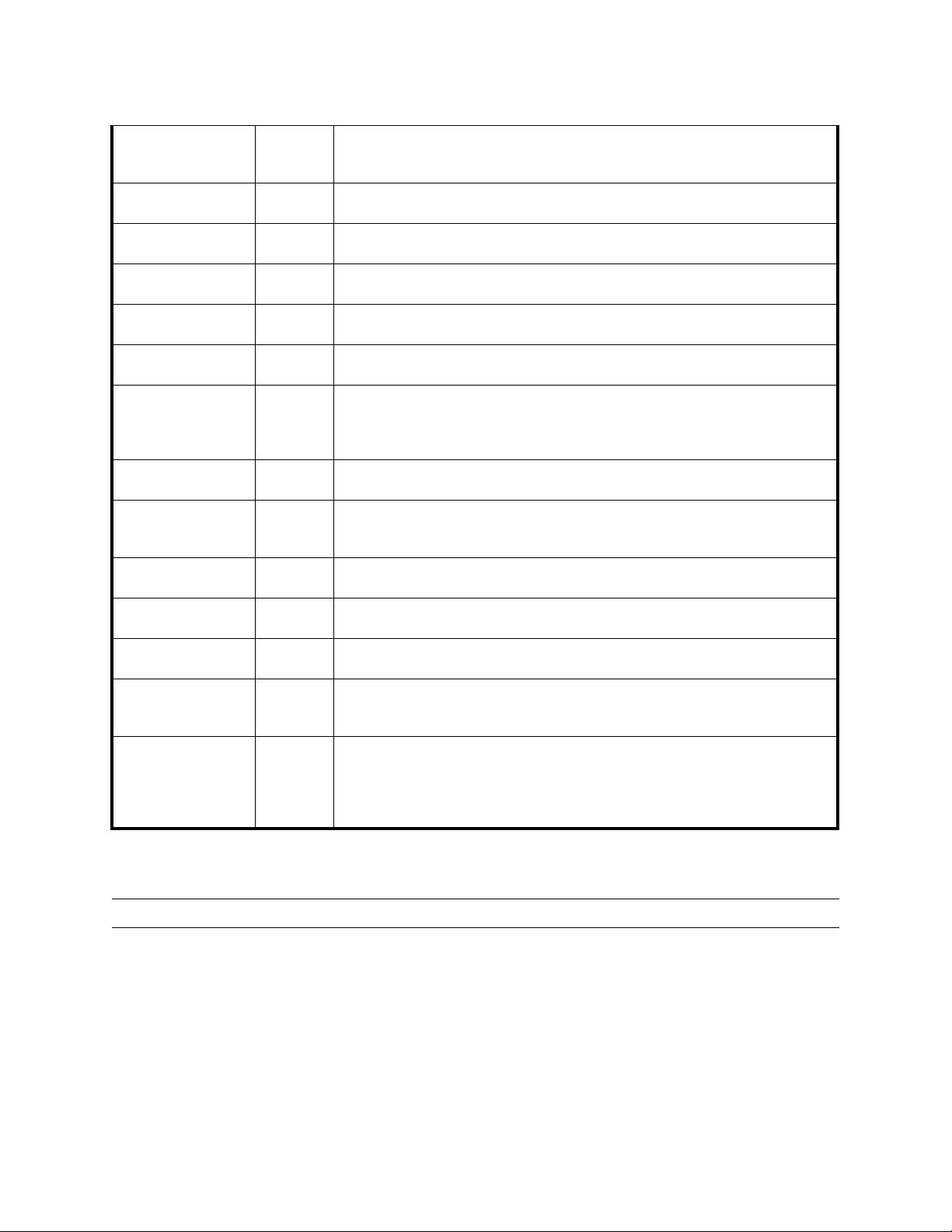

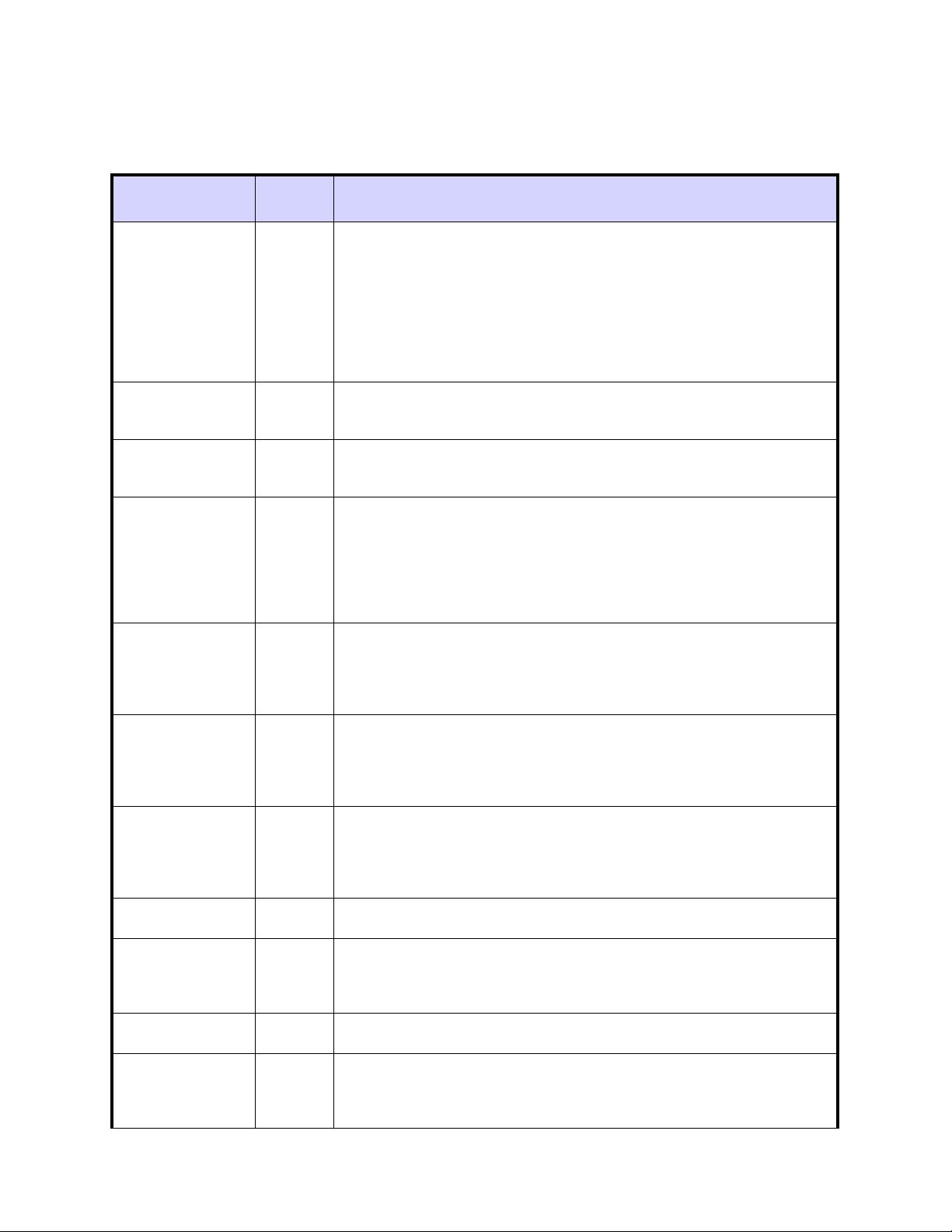

Table 1 — Pin description

Name

Input/

Output

Description

IO0 ~ IO7(~ IO15)

DQ0 ~ DQ7

DQ0_x ~ DQ7_x

I/O

DATA INPUTS/OUTPUTS

These signals are used to input command, address and data, and to output data

during read operations. The signals float to high-z when the chip is deselected or

when the outputs are disabled. IO0 ~ IO15 are used in a 16-bit wide target

configuration. With multi channel support, IO0_0~IO7_0 and IO0_1~IO7_1 are

used for IOs of channel 0 and IOs of channel 1 respectively. Also known as

DQ0~DQ7 for Toggle DDR and Synchronous DDR.

The number after the underscore represents the channel. For example, DQ0_0

indicates DQ0 of channel-0 and DQ0_1 does DQ0 of channel-1.

CLE_x I

COMMAND LATCH ENABLE

The CLE_x signal is one of the signals used by the host to indicate the type of

bus cycle (command, address, data).

ALE_x I

ADDRESS LATCH ENABLE

The ALE_x signal is one of the signals used by the host to indicate the type of

bus cycle (command, address, data).

CEx_x_n I

CHIP ENABLE

The CEx_x_n input is the target selection control. When CEx_x_n is high and

the target is in the ready state, the target goes into a low-power standby state.

When CEx_x_n is low, the target is selected.

The number after the first underscore represents the channel. For example,

CE0_0_n indicates CE0_n of channel-0 and CE0_1_n does CE0_n of channel-

1.

WE_x_n I

WRITE ENABLE

The WE_x_n input controls writes to the I/O port. For Asynchronous SDR Data,

commands, addresses are latched on the rising edge of the WE_x_n pulse. For

Toggle DDR commands, addresses are latched on the rising edge of the

WE_x_n pulse.

R/B_x_n O

READY/BUSY OUTPUT

The R/B_x_n output indicates the status of the target operation. When low, it

indicates that one or more operations are in progress and returns to high state

upon completion. It is an open drain output and does not float to high-z condition

when the chip is deselected or when outputs are disabled.

RE_x_n

(RE_x_t)

I

READ ENABLE

The RE_x_n input is the serial data-out control. For Asynchronous SDR Data is

valid tREA after the falling edge and for Toggle DDR Data is valid after the falling

edge & rising edge of RE_x_n which also increments the internal column

address counter by each one.

RE_x_c I

Complement of Read Enable

This is the complementary signal to Read Enable

DQS_x

(DQS_x_t)

I/O

Data Strobe

The data strobe signal that indicates the data valid window for Toggle DDR and

Synchronous DDR data interface. Output with read data, input with write data.

Edge-aligned with read data, centered in write data.

DQS_x_c I/O

Complement of Data Strobe

This is the complementary signal to Data Strobe.

W/R_x I

Write/Read Direction

The Write/Read Direction signal indicates the owner of the DQ bus and DQS

signal in the Synchronous DDR data interface. This signal shares the same pin

as RE_x_n in the asynchronous data interface.