18

DS90UB953-Q1

ZHCSGW1B –SEPTEMBER 2017 –REVISED SEPTEMBER 2018

www.ti.com.cn

版权 © 2017–2018, Texas Instruments Incorporated

7.3.1.6.2 CSI-2 Check Sum Detection

A CSI-2 long packet header contains a 16-bit check sum before the end of transmission. The DS90UB953-Q1

calculates the check sum of the incoming CSI-2 data. If a check sum error is detected, the check sum error

status will be saved in the CSI_ERR_STATUS register (0x5D) and can also be forwarded to the deserializer

through the bidirectional control channel.

7.3.1.6.3 D-PHY Error Detection

DS90UB953-Q1 detect and reports SoT and SoT Sync errors.

7.3.1.6.4 CSI-2 Receiver Status

For the Receive ports, several status functions can be tracked and monitored through register access. The status

indications are available for error conditions as well as indications of change in line length measurements. These

are available through the CSI_ERR_CNT (0x5C), CSI_ERR_STATUS (0x5D), CSI_ERR_DLANE01 (0x5E),

CSI_ERR_DLANE23 (0x5F), and CSI_ERR_CLK_LANE (0x60) registers.

7.3.2 FPD-Link III Forward Channel Transmitter

The DS90UB953-Q1 features a high-speed signal transmitter capable of driving signals at rates of up to 4.16

Gbps.

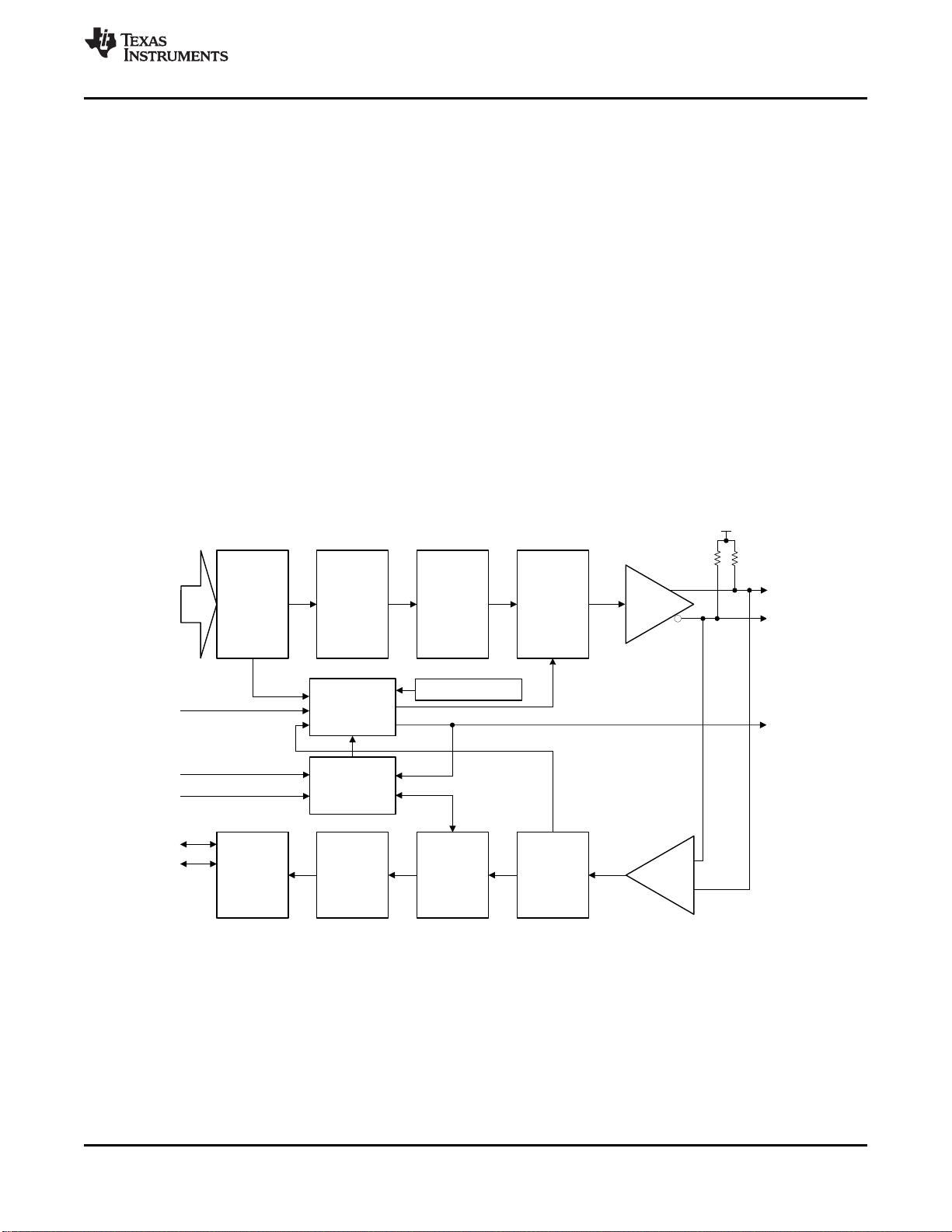

7.3.2.1 Frame Format

The DS90UB953-Q1 formats the data into 40-bit long frames. Each frame is encoded to ensure DC balance and

to ensure sufficient data line transitions. Each frame contains video payload data, I

2

C forward channel data, CRC

information, framing information, and information regarding the state of the CSI-2 interface.

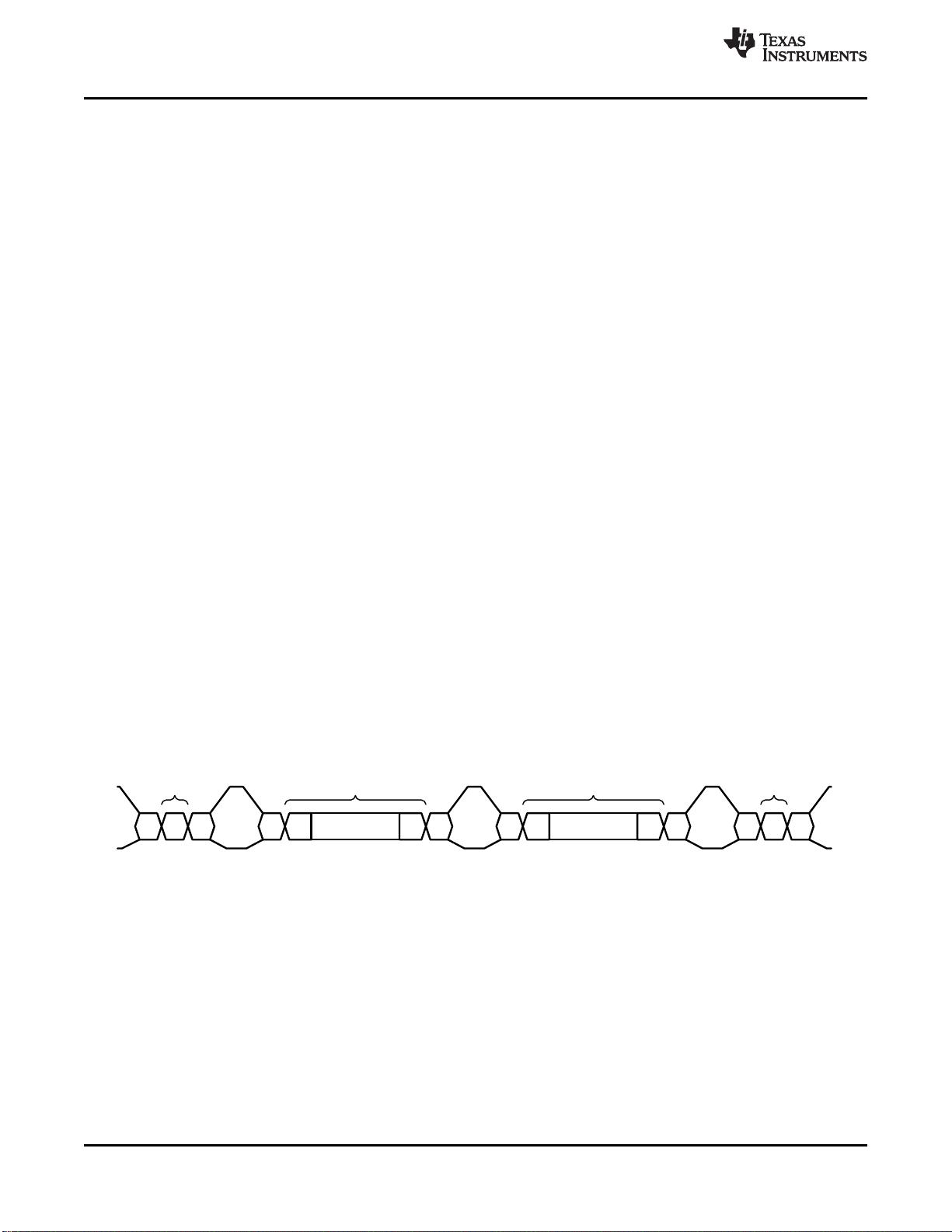

7.3.3 FPD-Link III Back Channel Receiver

The FPD-Link III back channel receives an encoded back channel signal over the FPD-Link III interface. The

back channel frame is a 30-bit frame that contains I

2

C commands and GPIO data. The back channel frame

receives an encoded clock and data from the deserializer, thus the data bit rate is one-half the frequency of the

highest frequency received.

The back channel frequency is programmable for operation with compatible deserializers. The default setting is

determined by the MODE strap pin. For operation with the DS90UB954-Q1 or DS90UB960-Q1, the back channel

should be programmed for 50-Mbps operation in DS90UB953-Q1 Synchronous mode and programmed for 10-

Mbps operation for non-synchronous modes.

7.3.4 Serializer Status and Monitoring

The DS90UB953-Q1 features enhanced FPD-Link III diagnostics, system monitoring, and Built-In Self Test

capabilities. It monitors forward channel and back channel data for errors and reports them in the status

registers. It also supports voltage and temperature measurement for system level diagnostics. The Built-In Self

Test feature allows testing of the forward channel and back channel data transmissions without external data

connections.

7.3.4.1 Forward Channel Diagnostics

The DS90UB953-Q1 monitors the status of the forward channel link. The forward channel high-speed PLL lock

status is reported in the HS_PLL_LOCK bit (Register 0x52[2]). When paired with the DS90UB954-Q1, the FPD-

Link III deserializer LOCK status is also reported in the RX_LOCK_DETECT bit (Register 0x52[6]).

7.3.4.2 Back Channel Diagnostics

The DS90UB953-Q1 monitors the status of the back channel link. The back channel CRC errors are reported in

the CRC_ERR bit (Register 0x52[1]). The number of CRC errors are stored in the CRC error counters and

reported in the CRC_ERR_CNT1 (Register 0x55) and CRC_ERR_CNT2 (Register 0x56) registers. The CRC

error counters are reset by setting the CRC_ERR_CLR (Register 0x49[3]) to 1.