Quartus2中的EDA与VHDL实验:二选一多路选择器与全加器设计

需积分: 9 151 浏览量

更新于2024-07-29

收藏 273KB DOC 举报

"EDA与VHDL课程实验,通过Quartus2进行数字电路设计和仿真,涉及组合电路、等精度频率计的相关知识。"

在电子设计自动化(EDA)领域,VHDL是一种广泛使用的硬件描述语言,用于设计和实现数字逻辑系统。本课程实验主要针对初学者,旨在让学生熟悉Quartus2软件的VHDL设计流程,包括文本编辑、电路仿真和硬件测试。实验分为两个部分,重点是组合电路的设计。

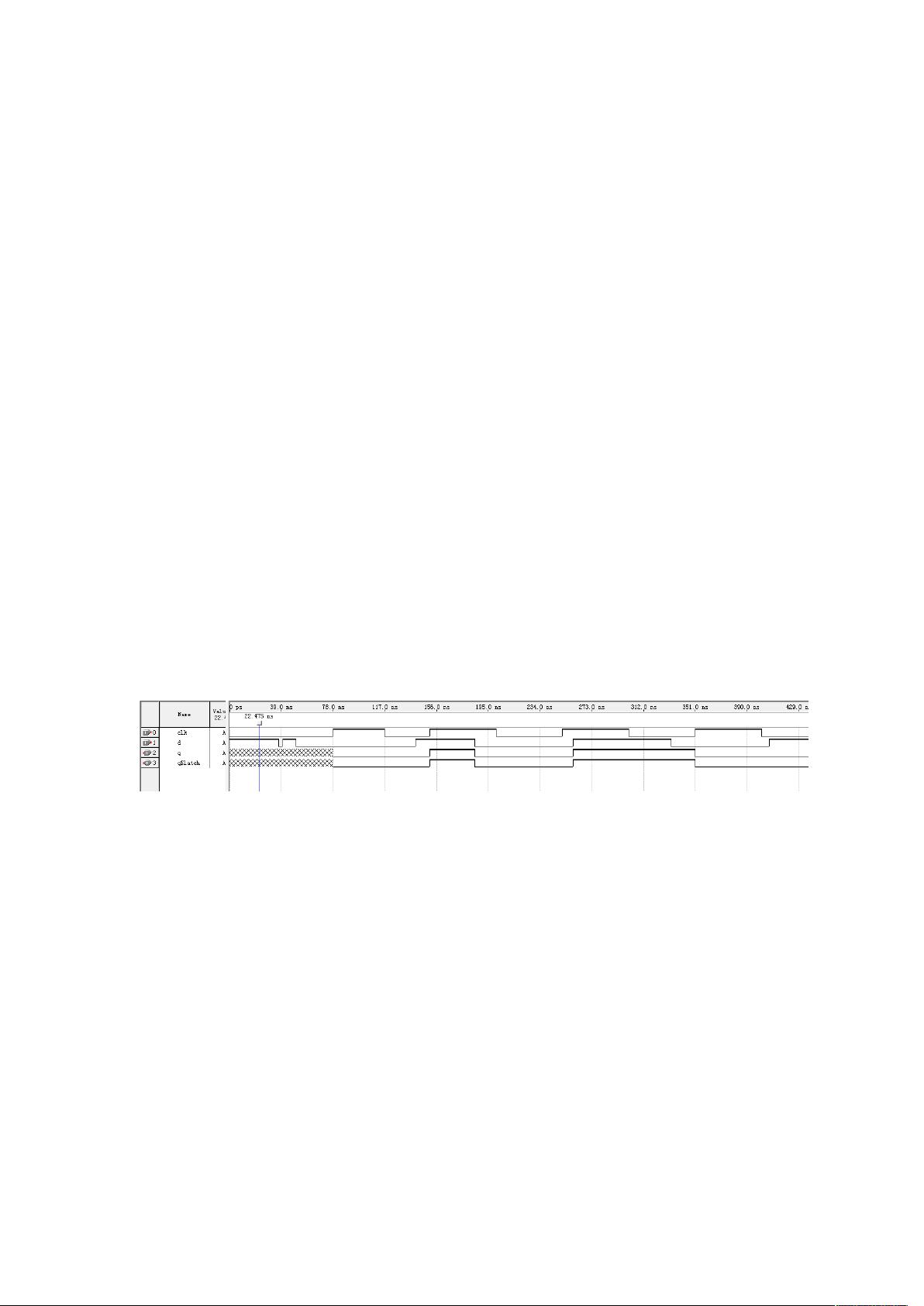

实验任务1是设计一个二选一多路选择器。二选一多路选择器是一种基础的数字逻辑组件,它根据输入控制信号`s`来选择输出为输入信号`a`或`b`。在VHDL中,这个组件被定义为一个实体(entity),其行为(architecture)是一个进程(process),在进程中判断`s`的状态,决定`y`的输出。仿真结果显示了在不同`s`状态下,`y`的预期输出,这验证了设计的正确性。在硬件测试阶段,该设计可以在实验系统上实际运行,以确认其在真实环境中的功能。

实验任务2则进一步扩展了组合逻辑设计,要求设计一个全加器,然后构建一个八位并行二进制加法器。全加器是一个可以处理进位的加法单元,它结合了两个二进制位和一个进位输入,生成和与进位输出。学生需要利用VHDL的例化语句(instance statement)将全加器作为基本元件,创建一个八位全加器的顶层文件。这个八位加法器可以同时处理八个二进制位的加法操作,其电路特性包括并行处理和进位传递。

图3-31的仿真程序可能是一个更复杂的系统,如一个带有进位的多位加法器,其中包含了多个二选一多路选择器和全加器实例。在这个系统中,输入`a`是一个四位二进制数,`s`是控制信号,而输出`y`是计算结果。仿真结果会展示在不同输入和控制条件下的电路行为。

通过这样的实验,学生不仅可以掌握基本的VHDL语法和设计流程,还能理解组合电路的工作原理,以及如何在实际硬件上验证设计。此外,实验还涉及到了模块复用和并行处理的概念,这些都是数字系统设计中的核心概念。对于理解和应用EDA工具,以及后续的FPGA或ASIC设计来说,这些知识都是非常关键的。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2014-12-10 上传

2024-11-30 上传

2024-11-30 上传

158 浏览量

2024-11-30 上传