ASIC设计精华:开发流程与关键技术解析

"ASIC牛人之经典总结"

ASIC(应用专用集成电路)是为特定功能而设计的集成电路,具有高效能、低功耗等优势。本文档深入探讨了ASIC设计的关键环节,提供了丰富的知识总结,适合对ASIC开发感兴趣的工程师阅读。

1. **ASIC设计流程**

- 准备需求规格:在设计开始前,明确芯片的功能、性能和功耗要求。

- 微架构文档创建:定义模块结构和功能接口。

- RTL设计与IP开发:使用硬件描述语言(如Verilog或VHDL)编写寄存器传输级(RTL)代码。

- 功能验证:确保所有IP核满足设计规范,通过linting检查和行为仿真来验证代码。

- 设计约束准备:包括时钟定义、输入/输出延迟、输出负载定义等。

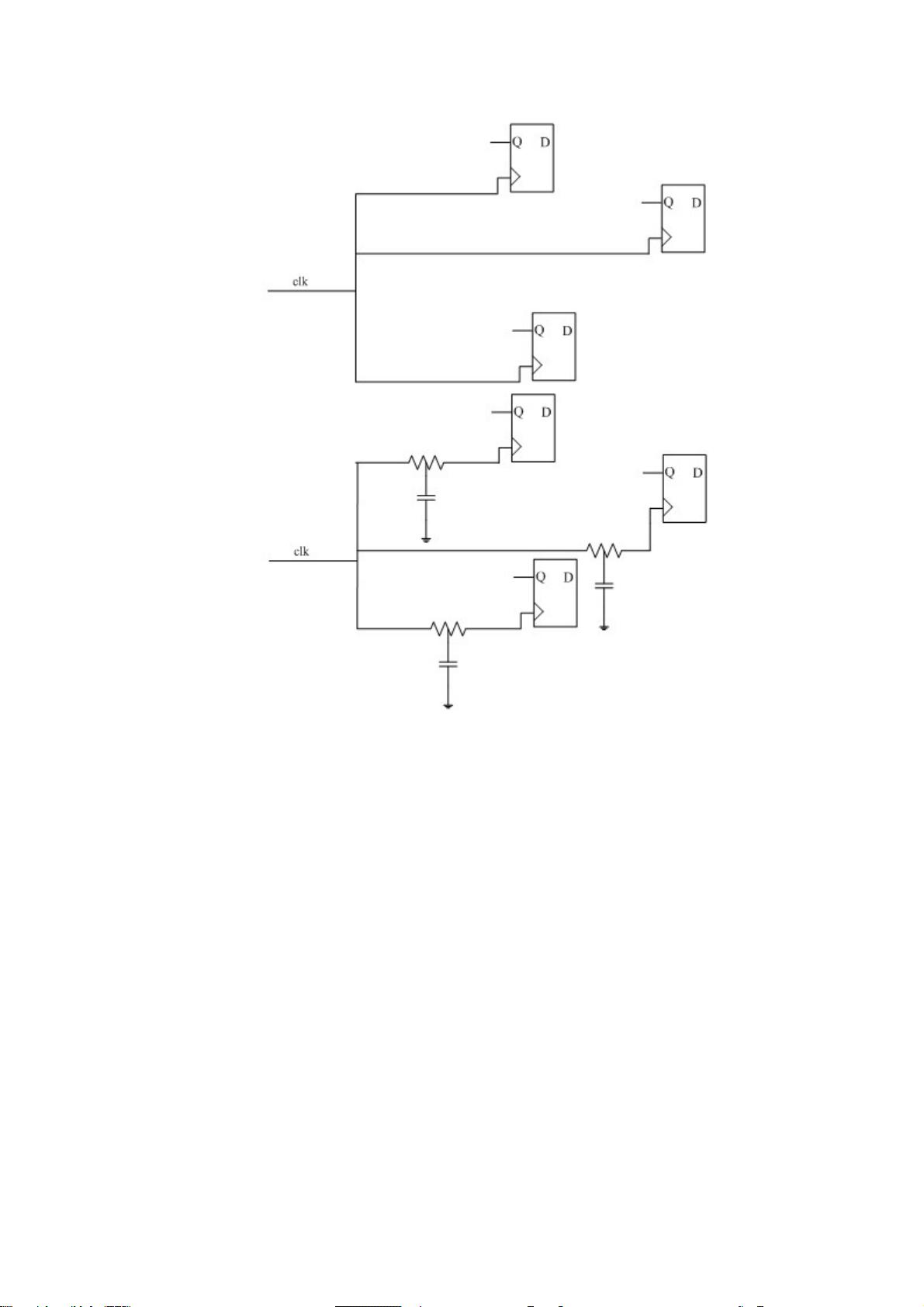

2. **时钟抖动(Clock Jitter)**

- 时钟抖动是时钟信号的时间不确定性,它影响电路的稳定性和可靠性。理解和控制时钟抖动对于高性能ASIC设计至关重要。

3. **信号同步**

- 在ASIC设计中,信号同步是确保数据在不同模块间正确传递的关键,涉及锁相环(PLL)、分频器等同步技术。

4. **数字后端流程**

- 这包括布局布线、时序分析、功耗计算等步骤,确保设计满足速度、面积和功耗目标。

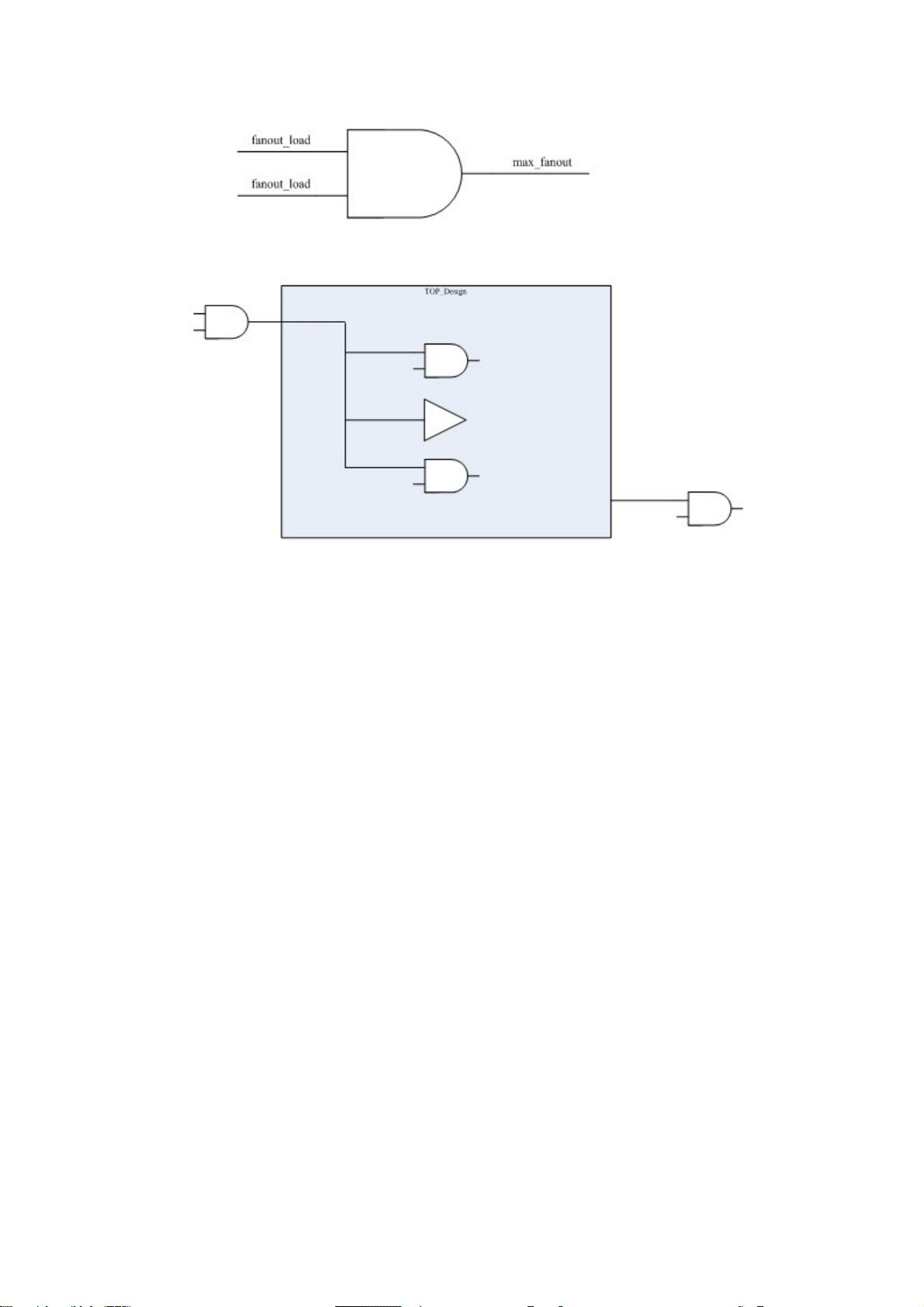

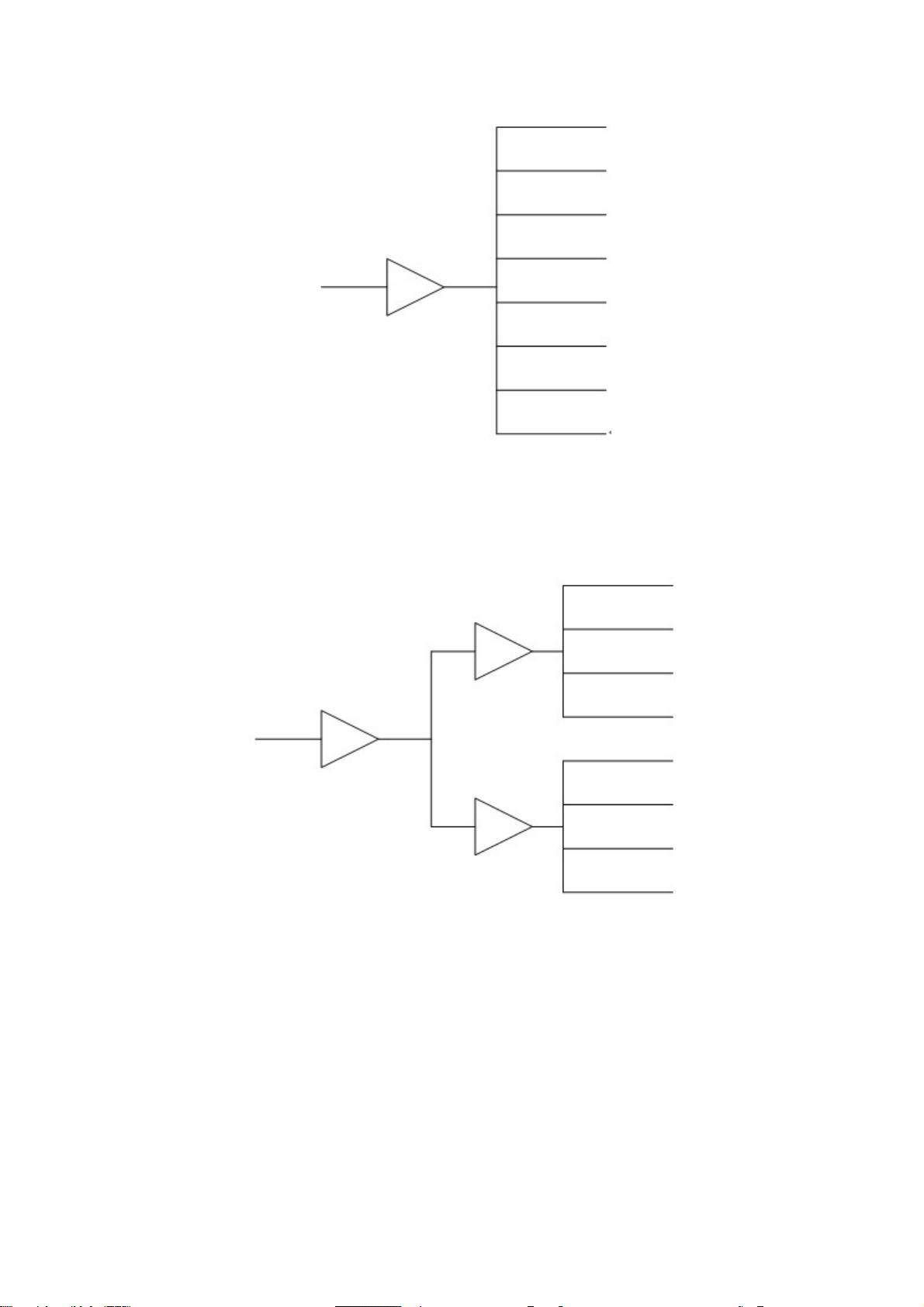

5. **Synopsys Design Compiler (DC)** 概论

- DC是一款综合工具,用于将RTL代码转换为门级网表。文中涵盖了setup time、hold time、fanout、skew、high fanout、multicycle path、gated clock等关键概念及其优化。

6. **功耗管理**

- 介绍门控时钟的基本概念,这是降低静态和动态功耗的有效方法。

7. **静态时序分析(Static Timing Analysis, STA)**

- STA是验证设计是否满足时序约束的关键工具,包括setuptime和holdtime分析,以及对FALSE PATH的理解。

8. **TimeQuest时钟分析**

- TimeQuest是另一款时序分析工具,提供高级时钟树分析和电源域分析功能。

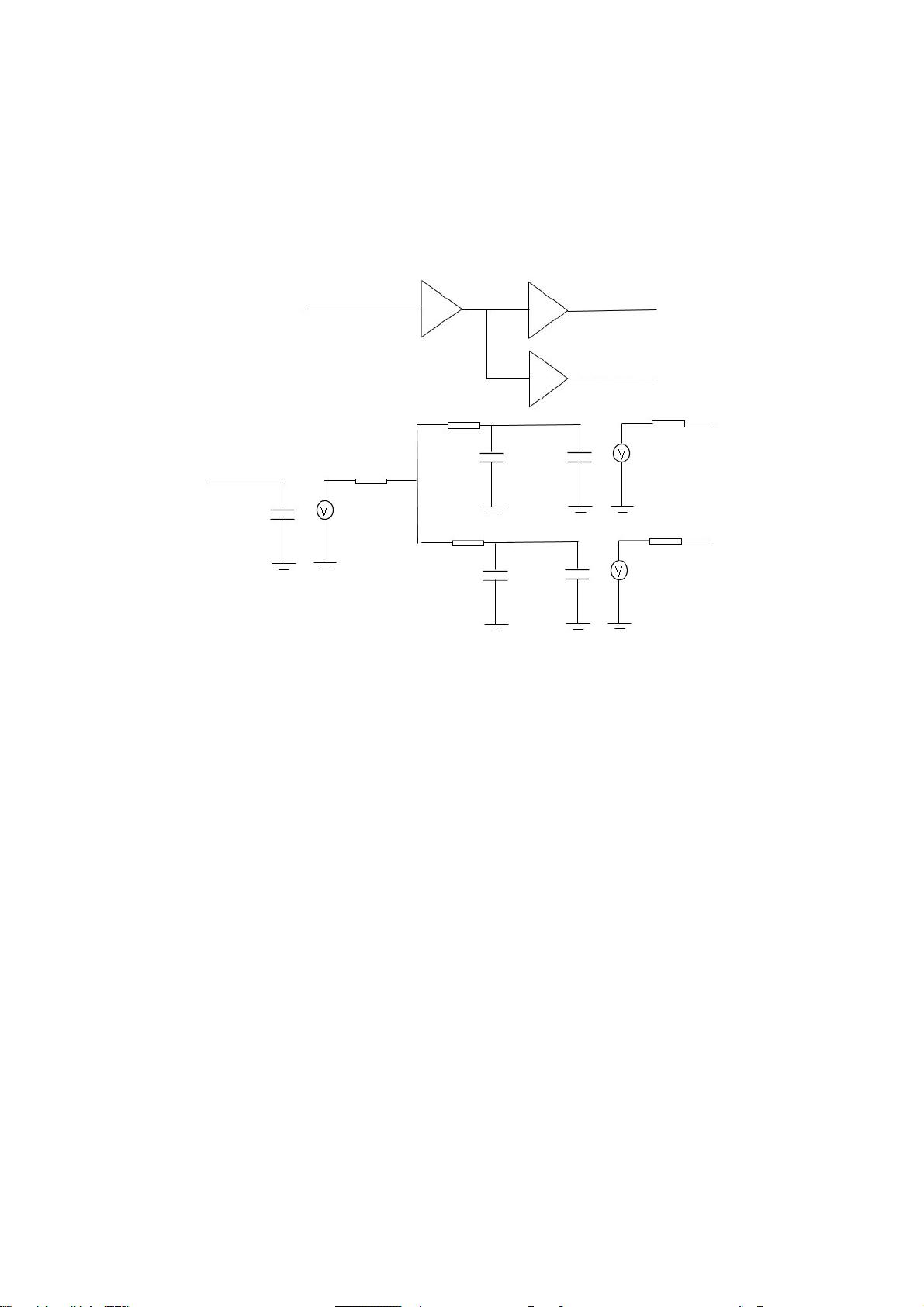

9. **寄生参数提取**

- 寄生参数影响实际电路性能,提取这些参数是进行静态时序分析的前提。

10. **IC设计流程及工具**

- 文档最后概述了整个IC设计流程,包括前端设计、物理设计、验证和流片等步骤,以及常用的工具链。

这个总结涵盖了ASIC设计的核心技术和实践,对于理解ASIC开发的全貌极具价值。通过深入学习和应用这些知识,开发者可以提高设计效率,确保ASIC的成功实现。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-11-12 上传

2011-01-16 上传

2022-08-03 上传

2020-08-13 上传

2021-10-07 上传

2024-11-29 上传

gpanyh

- 粉丝: 0

- 资源: 2

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍