FPGA实现:异步FIFO的设计与应用解析

需积分: 23 78 浏览量

更新于2024-09-08

收藏 346KB PDF 举报

"异步FIFO的FPGA实现"

异步FIFO在FPGA(Field-Programmable Gate Array)中的实现是一项关键的技术,用于解决多时钟域间的数据通信问题。FIFO,即First In First Out(先进先出)缓存器,是一种特殊的存储结构,其中的数据按照进入的顺序进行读取。在FPGA中,异步FIFO的实现尤其重要,因为它能够处理来自不同时钟域的数据流,确保数据的正确传输和同步。

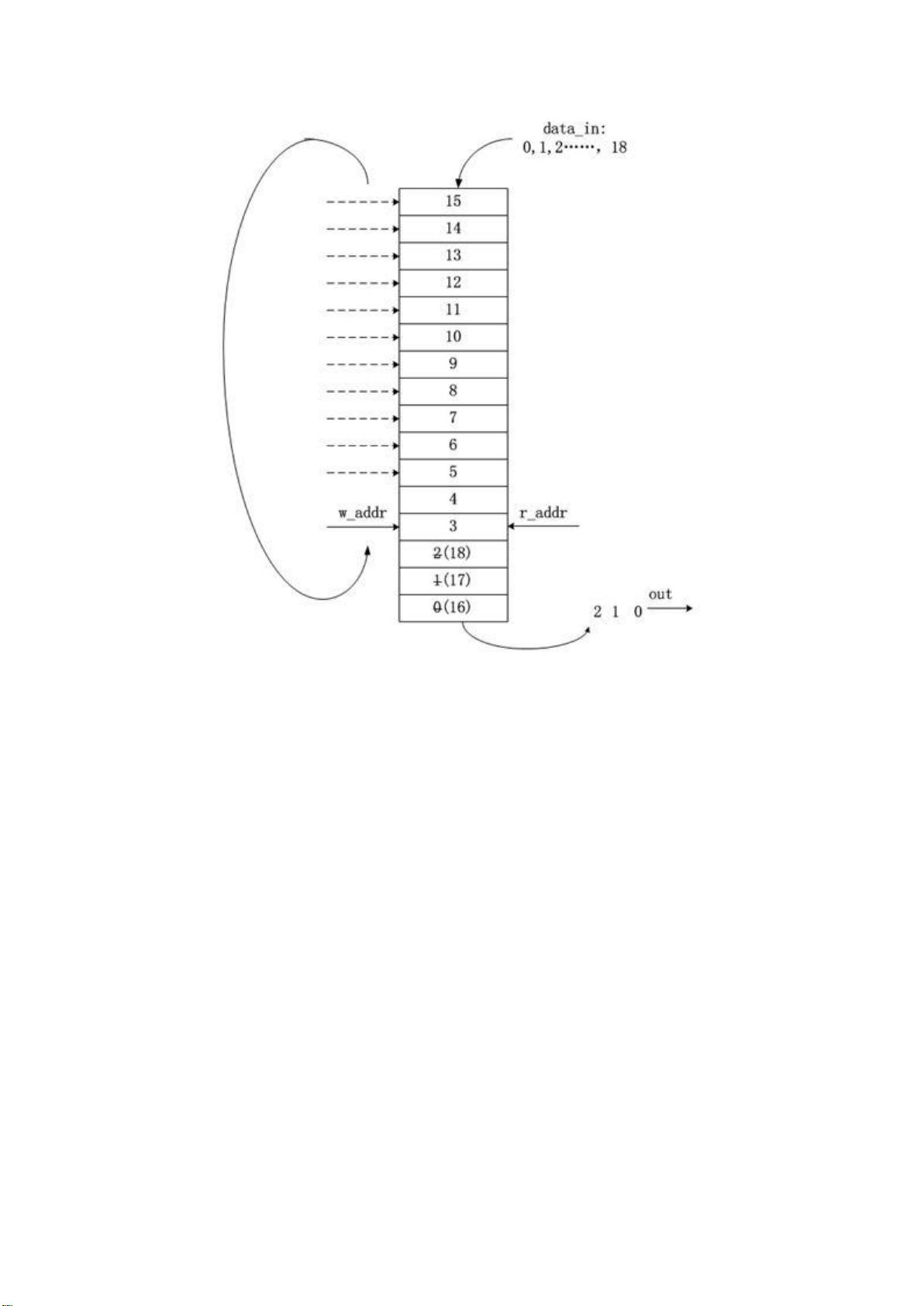

FIFO的基本工作原理是,通过内部的读写指针跟踪数据的位置。当数据写入FIFO时,写指针会递增;当数据被读出时,读指针也会递增。FIFO的宽度定义了每次读写操作的数据位数,而深度则决定了它可以存储多少个这样的数据单元。在异步FIFO中,读写操作并不受同一个时钟控制,它们各自有独立的时钟源,这就需要特别的同步机制来确保数据的正确流动。

在实际应用中,异步FIFO主要解决两个问题:

1. **异步时钟域间的接口设计**:在大型集成电路设计中,由于模块化和性能需求,往往存在多个不同的时钟域。异步FIFO提供了一个简单且高效的方式,能够在这些不同时钟域之间安全地传输数据,避免因时钟不同步导致的数据错误。

2. **数据宽度匹配**:不同设备或处理器可能具有不同的数据总线宽度。例如,8位的微控制器和16位的DSP之间进行数据交换时,可以使用FIFO来桥接数据宽度的差异,确保数据的正确传输。

异步FIFO的关键特性包括:

- **满标志**:当FIFO将要满时,会发出一个信号来防止更多的数据写入,以避免溢出(overflow)。

- **空标志**:当FIFO将要空时,会发送一个信号来阻止读操作,以免读取无效数据,防止下溢(underflow)。

- **读时钟**:读操作遵循的时钟,确保在正确的时钟边缘读取数据。

- **写时钟**:写操作遵循的时钟,保证在合适的时刻将数据写入FIFO。

在FPGA实现异步FIFO时,通常会使用 Gray码计数器和同步器来处理时钟域的边界问题。Gray码计数器可以减少时钟转换时的毛刺,同步器则用来消除时钟域之间的亚稳态,确保数据的准确传递。此外,状态机和控制逻辑会监控FIFO的状态,并根据满标志和空标志来调整读写操作。

异步FIFO在FPGA设计中扮演着至关重要的角色,它的核心在于如何在不同时钟域中有效地管理和传输数据,同时确保系统的稳定性和可靠性。理解和掌握异步FIFO的设计原理和实现方法,对于FPGA开发者来说是至关重要的。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-12-23 上传

2020-08-01 上传

2009-03-23 上传

2015-06-09 上传

2021-01-19 上传

2021-07-13 上传

liujiejcomeon

- 粉丝: 1

- 资源: 1

最新资源

- 上市公司绿色专利数据1985-2019

- awesome-robotic-tooling:带有ROS,自动驾驶和航空航天技术的C ++和Python专业机器人开发工具:https:freerobotics.tools

- matlabransac代码-Final:最终项目

- react-wxsdk:基本react的微信帮助类

- condominio-app:公寓管理

- 仓库后端

- WeatherMan:使用kotlin学习Android应用程序开发(Goobar-面向初学者的9周Android开发课程)

- csv2json:另一个用Go编写的CSV到JSON的CSV转换器

- 数学建模-离散模型.zip

- 基于RPC的MapReduce简单实现.zip

- Ahq-ch-crx插件

- django-subadmin:一种特殊的ModelAdmin,它可以嵌套在另一个ModelAdmin中

- 我的bug 禅道项目管理软件源码

- python_basic

- treeshaking:使用汇总和Webpack探索树木摇晃4

- one-front:一个网页版