异步FIFO设计与FPGA实现技术解析

需积分: 9 193 浏览量

更新于2024-09-13

收藏 416KB DOC 举报

"异步FIFO结构及FPGA设计"

异步FIFO(First In First Out)是电子设计中用于解决多时钟域数据传输的关键技术。在现代集成电路中,由于设计复杂度增加,常常存在多个不同的时钟域,而异步FIFO则作为一个高效的接口,确保在这些异步时钟域之间能够可靠地传输数据,特别是在网络接口和图像处理等领域应用广泛。

异步FIFO的基本结构通常包含双端口RAM作为存储介质,允许在同一时间进行读写操作。双端口RAM有两个独立的访问端口,分别对应于读时钟域和写时钟域。在写时钟域,数据被写入,由写地址产生逻辑生成写控制信号和写地址。而在读时钟域,数据被读出,由读地址产生逻辑生成读控制信号和读地址。此外,空/满标志的产生通过比较读写地址来实现,以监控FIFO的状态。

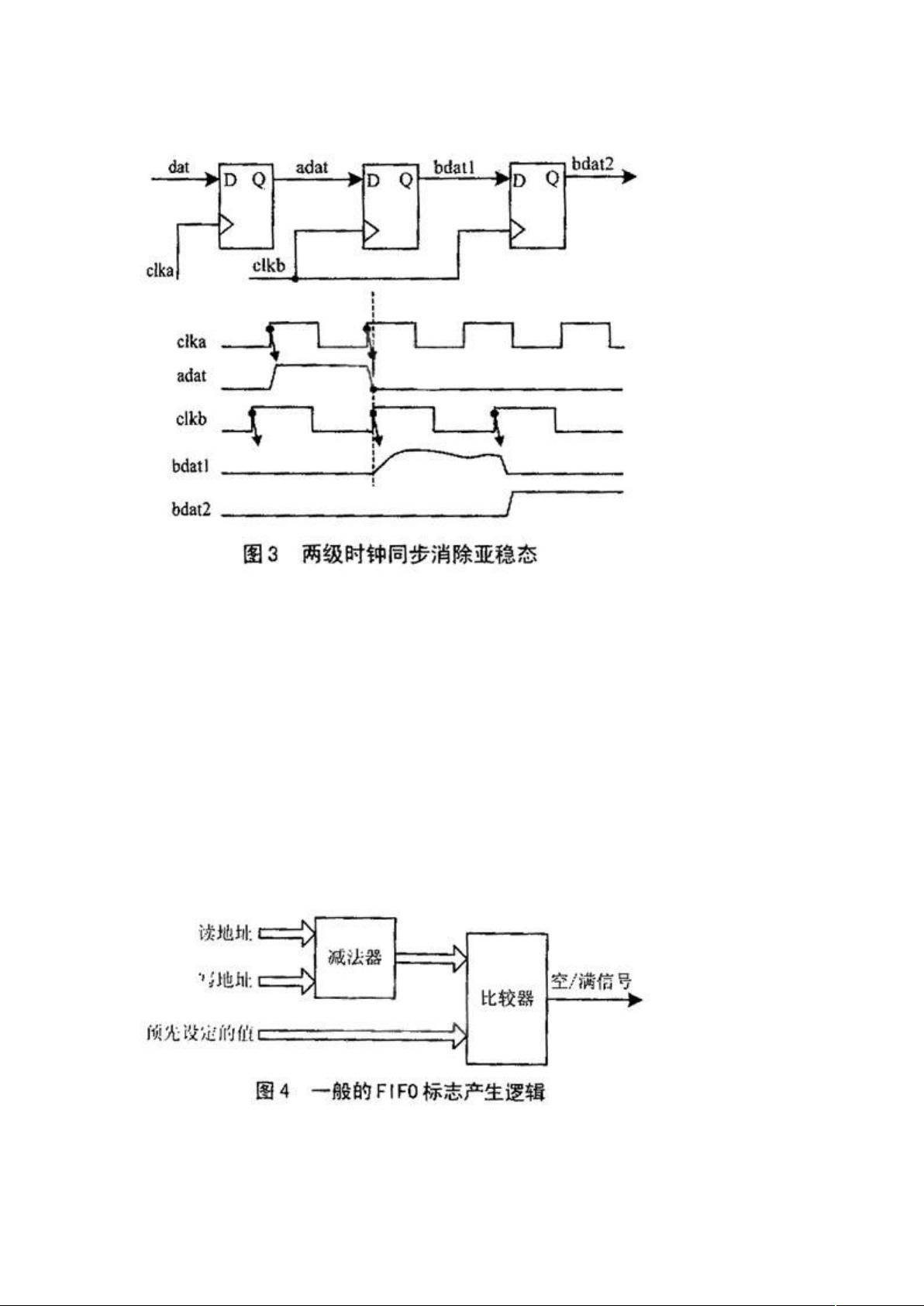

设计异步FIFO面临的主要挑战是解决异步信号同步和正确设计状态指示信号。首先,亚稳态问题是一个关键难题。亚稳态指的是在不满足时钟的建立/保持时间要求时,信号在触发器中产生的不稳定状态。这种状态可能导致数据错误,因为它会在不确定的时间点稳定到高电平或低电平。解决亚稳态的方法通常涉及使用同步器,即多个阶段的寄存器链,以增加亚稳态自我恢复的时间,确保在数据稳定后再被采样。

其次,正确设计空、满和几乎满的信号控制电路至关重要。这些状态指示器提供关于FIFO当前容量的信息,防止读写操作的错误发生。例如,当读写地址相等时,表示FIFO为空;而当读地址接近写地址,表明FIFO几乎满,需要谨慎处理,避免数据丢失。

在FPGA实现中,设计师通常会利用硬件描述语言(如VHDL或Verilog)来描述异步FIFO的逻辑,并通过综合工具将其转化为适配特定FPGA架构的门级网表。综合后的设计需要经过仿真验证,确保在各种条件下都能正确工作。在实际应用中,FPGA的可编程性使其成为实现异步FIFO的理想平台,可以根据具体需求调整设计,优化性能和资源利用率。

异步FIFO是解决多时钟域间数据传输的关键组件,其设计涉及到复杂的同步问题和状态管理。通过理解亚稳态的原理和控制电路的设计,以及借助现代FPGA技术,可以实现高效、可靠的异步数据接口。

144 浏览量

点击了解资源详情

613 浏览量

2010-11-01 上传

108 浏览量

2011-03-01 上传

231 浏览量

613 浏览量

130 浏览量

主打天空之城

- 粉丝: 2

- 资源: 13

最新资源

- 深圳市民网整站程序 V3.0

- To-Do:一个Web应用程序,允许用户创建根据几个项目组织的待办事项列表

- VCS操作所用到的文件

- bangai-o-sploit

- generate-api

- 通讯应用

- 物料&库位卡

- python自动答题脚本.zip

- weather-ring

- 85283857572802圣诞树.zip

- stunning-gnome-de:工具,配置,主题等,使GNOME DE看起来很棒

- 平台质量检查

- .NET C#控制台 Asp.net HTTP服务器端和客户端.zip

- use-reaction:对基于挂钩的模块化商店管理器框架做出React

- tecweb2021

- spring-boot-study:Spring Boot 入门教程及示例代码-源码