异步FIFO结构与FPGA实现策略:挑战与解决方案

60 浏览量

更新于2024-09-05

收藏 336KB PDF 举报

异步FIFO结构及FPGA设计

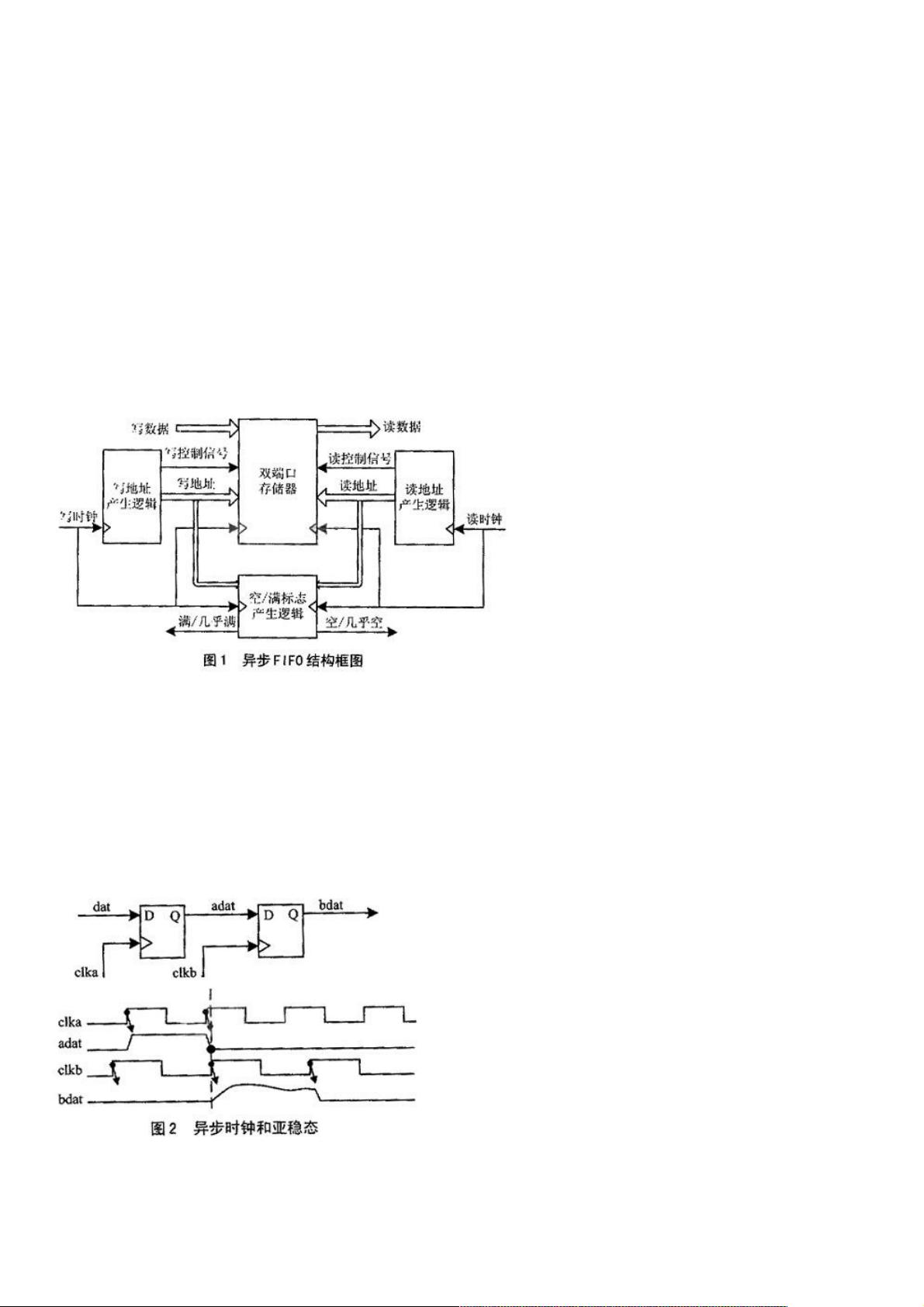

异步FIFO,全称First-In-First-Out(先进先出),是解决多时钟域系统中数据传输问题的关键组件。它在现代集成电路设计中扮演着重要角色,特别是在网络接口和图像处理等需要实时数据交换的场合。异步FIFO的主要作用是在不同时钟周期和相位的系统间提供稳定的数据缓冲和传输,确保数据的可靠传输。

设计异步FIFO的核心难点主要包括两个方面:

1. 亚稳态问题:由于异步时钟之间的不匹配,可能会导致触发器在信号被锁存时出现亚稳态现象。亚稳态是指触发器的输出在时钟上升沿之前或之后的不确定状态,可能导致数据错误。为解决这个问题,设计者需确保触发器满足setup/hold时间要求,即信号到达触发器输入的时间必须在时钟上升沿之前和之后的特定时间范围内,以避免亚稳态的产生。

2. 空/满控制电路设计:另一个挑战是正确设计空闲(空)、满和接近满的标志电路。这些信号对于异步FIFO的读写操作至关重要,需要精确控制进出数据的流程,防止数据溢出或丢失。

在设计上,通常采用双端口RAM作为存储介质,其允许在写时钟和读时钟域同时进行操作。通过写地址和读地址产生的逻辑控制信号,分别管理数据的写入和读取,同时利用空/满标志来监控存储空间的状态。在FPGA实现时,需要进行详细的逻辑设计、综合仿真,以验证电路的功能性和性能。

在本文中,作者不仅介绍了异步FIFO的基本概念,还提出了一种新颖的电路结构来克服上述难点,并进行了综合仿真和FPGA验证。这种设计旨在提高异步FIFO的可靠性与速度,使之能够在复杂的多时钟域环境中高效稳定地工作。通过对这些问题的深入研究和实践,设计师可以更好地应对现代集成电路设计中的时钟同步挑战。

2011-03-01 上传

109 浏览量

2012-10-30 上传

232 浏览量

613 浏览量

130 浏览量

2021-07-13 上传

145 浏览量

173 浏览量

weixin_38524246

- 粉丝: 6

- 资源: 920

最新资源

- python代码自动办公 Excel_更灵活的操作方式 项目源码有详细注解,适合新手一看就懂.rar

- 基于基于粒子滤波器的SLAM算法实现地图的成像matlab仿真

- 《鬼鬼盯着你》绘本故事PPT模板

- alfabetizar.aprender.digital

- 紫色花朵 潮流壁纸 高清风景 新标签页 主题-crx插件

- hveto_graph:hveto 摘要页面的 D3.js 版本

- who-does-not-follow-me:一个Node.js脚本,用于检查谁没有在GitHub上关注您

- CSS3地图热点文字标注提示特效代码

- python代码自动办公excel处理实例(单工作簿拆分到多工作簿中(多表中) 项目源码有详细注解,适合新手一看就懂.rar

- 对tabcontrol的应用及tabpage的处理

- emv:EMV芯片和PIN库

- giffus:一个允许用户通过互联网发送礼物的小型社交应用程序。 支持音乐等多种类型的礼物,特别是打开礼物,接收者必须去发送者想要的地方

- github-repos-react:添加GitHub repos并查看其详细信息和问题

- Khayyam-crx插件

- smoothing(imagetosm_ooth)_滤波_去噪_通信去噪_

- 局域网 【飞秋】 【FeiQ】 下载