Vivado配置ZYNQ工程详解

需积分: 0 153 浏览量

更新于2024-06-30

收藏 9.29MB DOCX 举报

"ZYNQ配置教程,基于Vivado 2018.3版本,涉及硬件描述文件HDF的生成以及ZYNQ FPGA核心的配置,包括工程创建、Block Design搭建、IP核的选择与定制,特别是针对米尔电子模板的运用。"

本文将详细介绍如何在Vivado环境下配置ZYNQ项目,主要针对的是ZYNQ FPGA的初步设计流程,以Vivado 2018.3版本为例。首先,我们需要创建一个新的工程。在启动Vivado后,选择"create project"选项,输入工程名称和保存路径。特别需要注意的是,路径中不能包含中文字符,否则可能导致Vivado无法识别,同时避免路径过长,以防止可能出现的问题。

接下来,进入工程创建向导的后续步骤,选择RTL Project,然后一路Next直到完成。在选择芯片部分,需设定速度等级为-1,封装为clg400,选定XC7Z020CLG400-1作为开发板芯片,最后点击Finish结束设置。

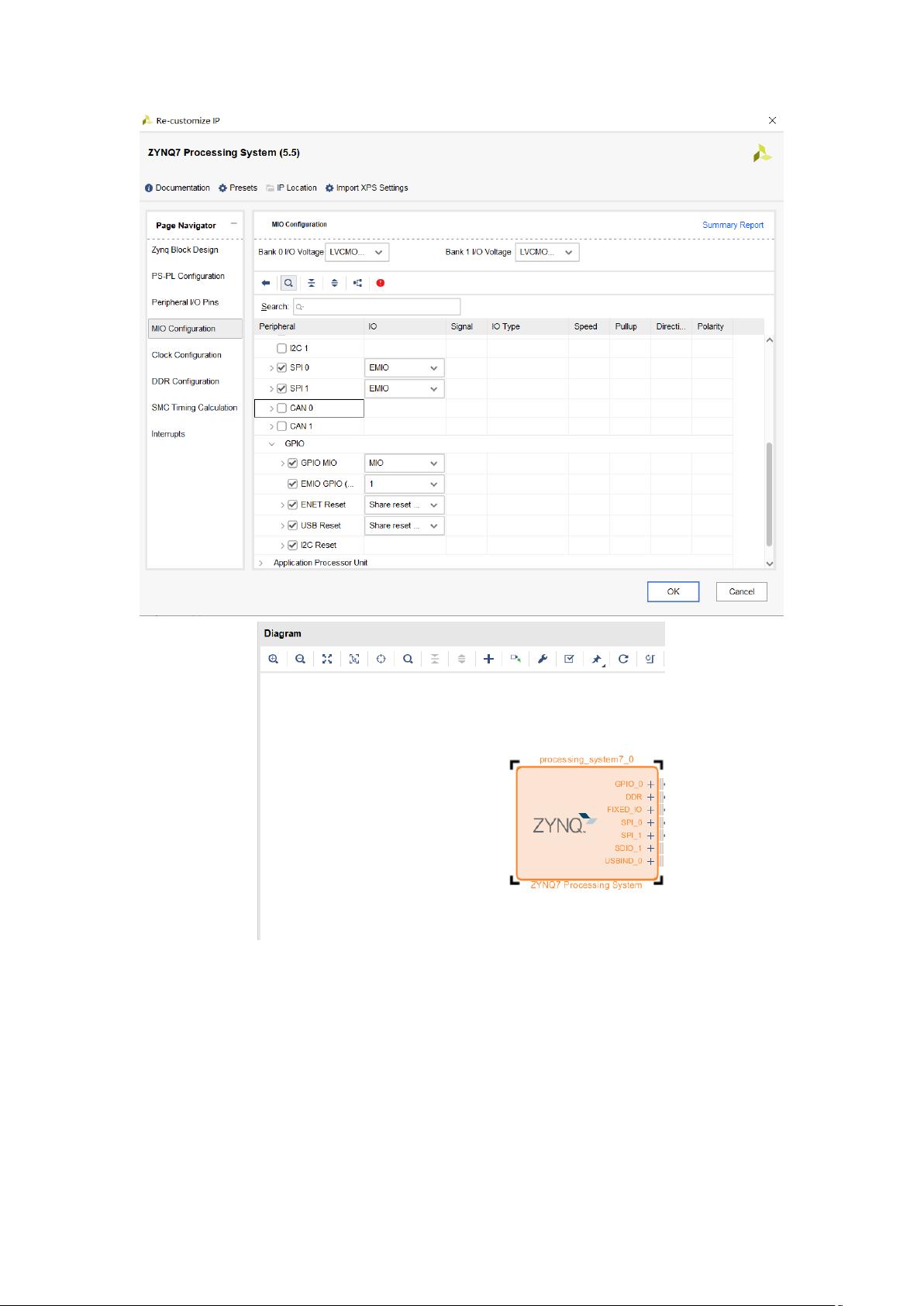

进入Block Design阶段,这是Vivado中的关键环节,用于构建硬件描述。首先创建新的Block Design文件,然后通过添加IP核来构建系统。搜索并添加ZYNQ IP核,双击后在Presets中应用配置。这里,我们参考米尔电子提供的MYIR.tcl模板,将该文件放在工程文件夹外的根目录下。在IP核设置中,确保勾选了所需的外设接口,如QuadSPI Flash、Ethernet0、USB0、SD0、SD1、UART1、SPI0、SPI1和GPIO等,即使某些接口实际未使用,也要进行配置。

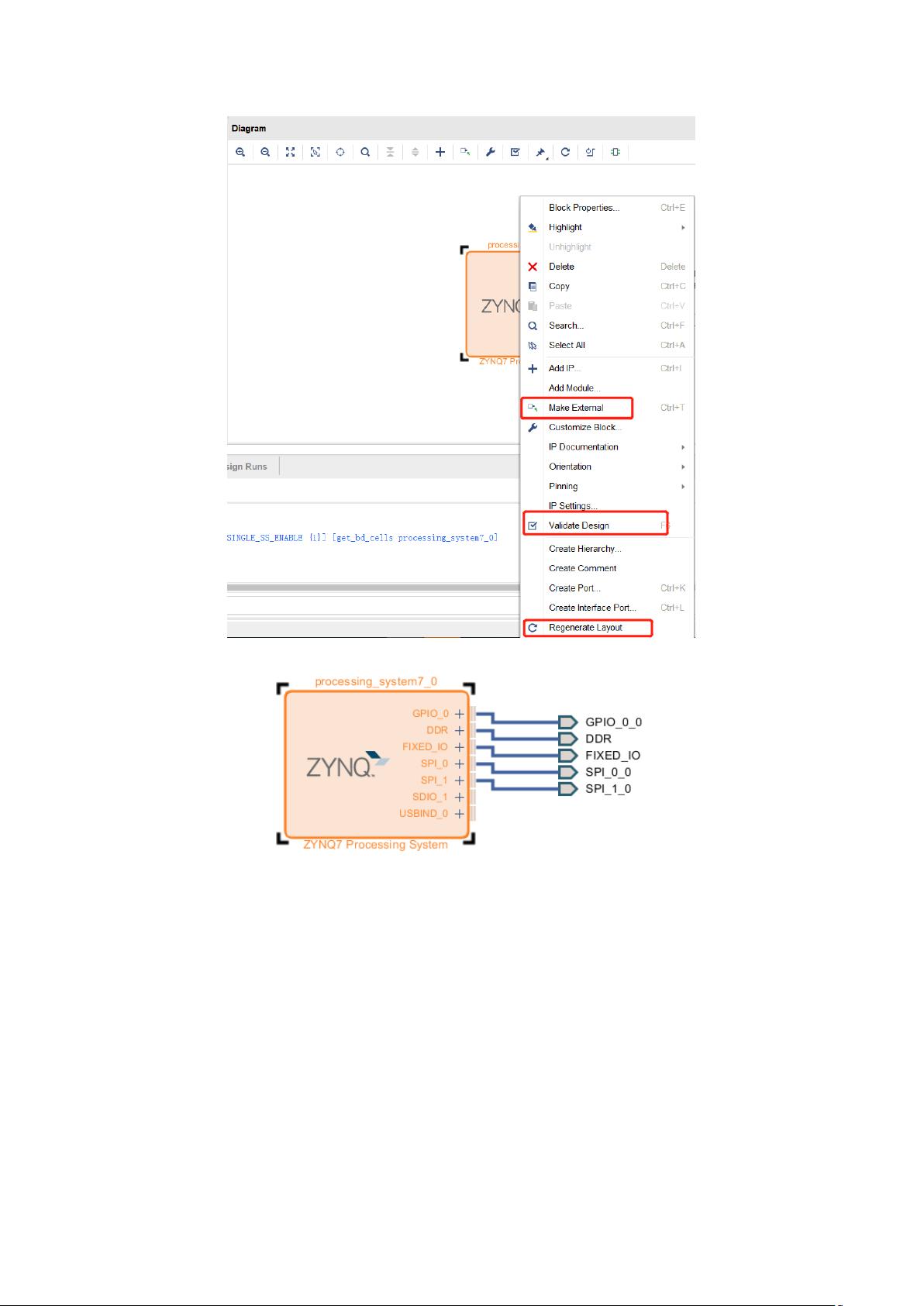

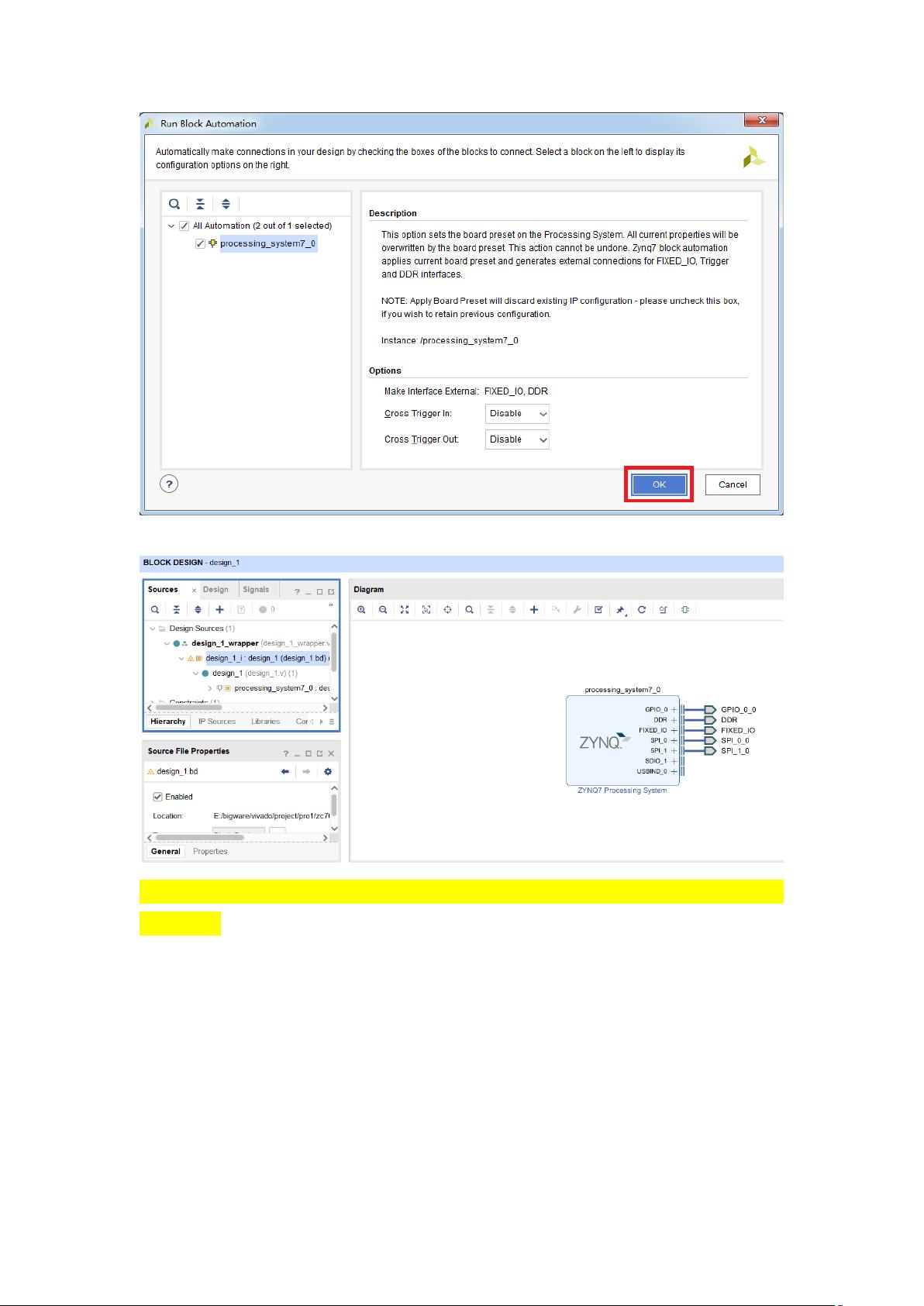

接着,右键点击ZYNQ IP核,选择"Make External"来生成外部接口,并删除不需要的SDIO_1和USBIND_0接口。配置完成后,运行Block Automation自动连接所有IP核,如果有任何改动,记得验证设计(Validate Design)和重新布局(Regenerate Layout)。最后,生成HDL Wrapper文件,这一步将为Block Design创建一个硬件描述层,以便于软件开发。

每个工程模板的配置可能略有不同,如果需要,可以利用constant块来连接外部IP核。完成上述步骤后,一个基本的ZYNQ FPGA设计就搭建完成了,接下来可以进行硬件仿真、综合、实现和下载到FPGA中进行实际测试。

总结来说,配置ZYNQ项目涉及到Vivado的工程创建、Block Design的搭建以及IP核的定制,这些步骤对于理解和掌握FPGA设计流程至关重要。对于初学者,熟练掌握这一流程将为后续的嵌入式系统开发打下坚实基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-02-27 上传

2022-06-15 上传

2015-10-27 上传

2024-07-19 上传

2024-01-12 上传

2024-12-26 上传

陌陌的日记

- 粉丝: 18

- 资源: 318

最新资源

- 全新PHP网址缩短防封短网址生成系统

- Almayce Video Handler-开源

- NotaFiscalNet:.NET电子发票生成

- 武汉医保读卡DLL动态库.rar

- Ziplyne Player prod-crx插件

- RestWithSpringBootMath

- ZoomTest.rar_FlashMX/Flex源码_FlashMX_

- Weinview触摸屏-OMRON_CJ1CS1PLC连接说明书

- quantcs-impl:量化类约束的实现

- Luiz_Henrique_Souza_JAMStackAlura

- paixu.rar_汇编语言_Asm_

- Learn-wp-cli:命令行,WP-CLI和自定义WP-CLI命令入门

- Ledavio Image Importer-crx插件

- The-ABM-in-Archaeology-Bibliography:有关考古中基于代理的模型(ABM)的文献的完整列表。 由Iza Romanowska和Lennart Linde维护和创建

- HubCollections.3okat1n89t.gaJP44e

- flexx:用纯Python编写桌面和Web应用程序