FPGA数字电路设计经验总结:时序设计的关键

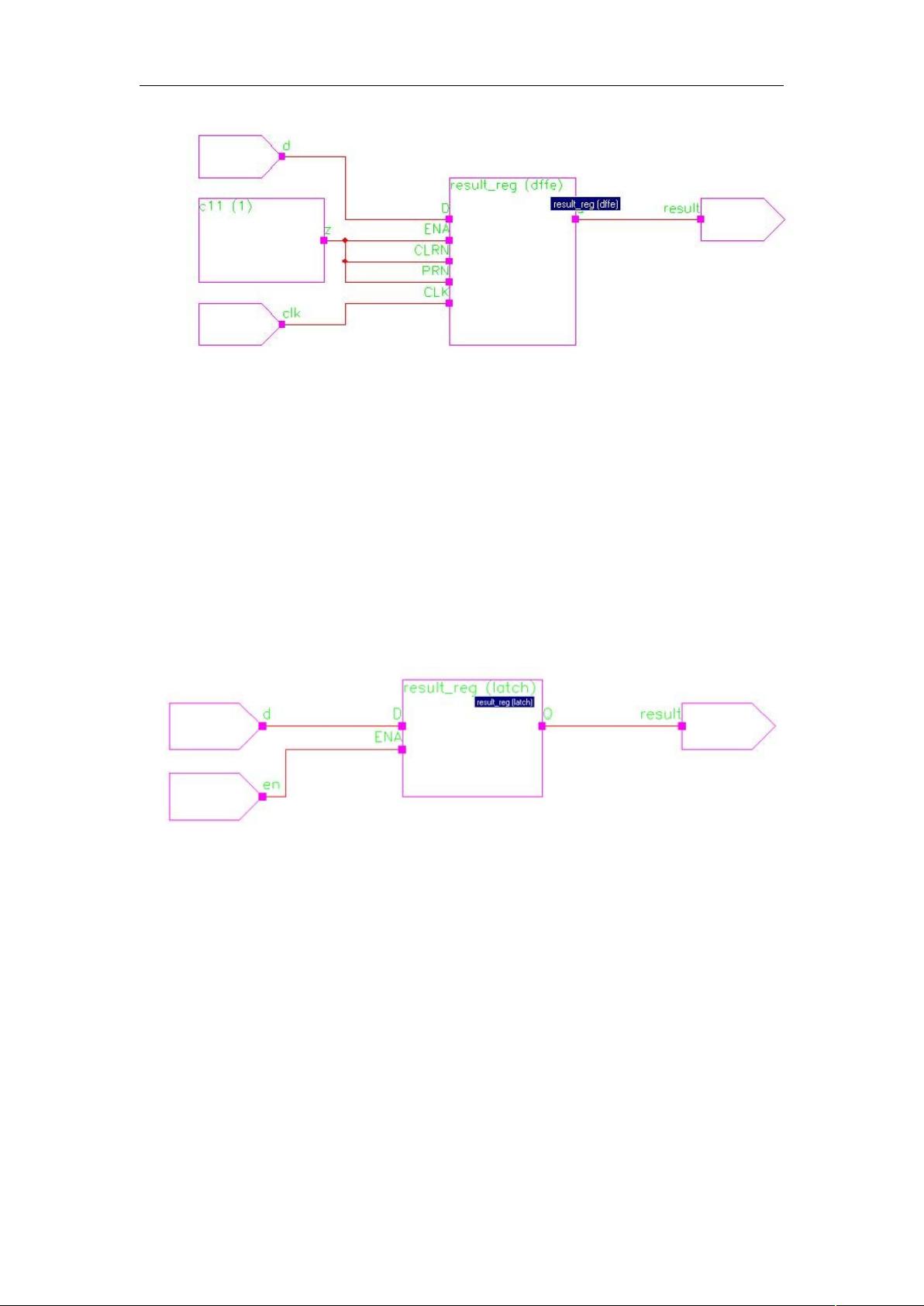

FPGA经验总结 FPGA/CPLD数字电路设计经验分享 在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握。但是,在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。 时序设计是数字电路设计的关键组成部分,对时序的控制是保证系统正确工作的前提。时序设计的难点在于它需要考虑到各个组件之间的时序关系,包括触发器的时序关系、数据传输的时序关系、时钟信号的时序关系等。因此,时序设计需要具备深入的知识和经验,才能正确地设计出高性能的数字电路系统。 在FPGA设计中,时序设计的重要性更是不可忽视。FPGA器件的高集成度和可编程性,使得时序设计变得更加复杂。因此,FPGA设计者需要具备深入的时序设计知识和经验,才能正确地设计出高性能的FPGA系统。 在FPGA设计中,时序设计的难点还在于它需要考虑到器件的制造工艺、工作电压、温度等条件的影响。这些条件对时序设计的影响是非常大的,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 在FPGA设计中,时序设计的重要性还在于它需要考虑到时钟树的偏斜情况。在FPGA器件中,时钟树的偏斜情况对时序设计的影响是非常大的。因此,设计者需要具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 时序设计的另一个难点是它需要考虑到建立时间和保持时间的要求。在FPGA设计中,建立时间和保持时间是两个非常重要的参数,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 在FPGA设计中,时序设计的难点还在于它需要考虑到器件的竞争和冒险现象。在FPGA器件中,器件的竞争和冒险现象对时序设计的影响是非常大的,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 时序设计是FPGA设计的关键组成部分,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。在FPGA设计中,时序设计需要考虑到各种因素的影响,包括器件的制造工艺、工作电压、温度等条件,时钟树的偏斜情况,建立时间和保持时间的要求,器件的竞争和冒险现象等。 在FPGA设计中,时序设计需要具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。因此,FPGA设计者需要不断学习和掌握新的时序设计知识和经验,才能不断提高设计水平和效率。 在FPGA设计中,时序设计需要考虑到器件的制造工艺、工作电压、温度等条件的影响。这些条件对时序设计的影响是非常大的,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 时序设计的另一个难点是它需要考虑到器件的竞争和冒险现象。在FPGA器件中,器件的竞争和冒险现象对时序设计的影响是非常大的,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 时序设计是FPGA设计的关键组成部分,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。在FPGA设计中,时序设计需要考虑到各种因素的影响,包括器件的制造工艺、工作电压、温度等条件,时钟树的偏斜情况,建立时间和保持时间的要求,器件的竞争和冒险现象等。 在FPGA设计中,时序设计需要具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。因此,FPGA设计者需要不断学习和掌握新的时序设计知识和经验,才能不断提高设计水平和效率。 时序设计的另一个难点是它需要考虑到器件的时序模型。在FPGA器件中,器件的时序模型对时序设计的影响是非常大的,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 时序设计是FPGA设计的关键组成部分,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。在FPGA设计中,时序设计需要考虑到各种因素的影响,包括器件的制造工艺、工作电压、温度等条件,时钟树的偏斜情况,建立时间和保持时间的要求,器件的竞争和冒险现象等。 在FPGA设计中,时序设计需要具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。因此,FPGA设计者需要不断学习和掌握新的时序设计知识和经验,才能不断提高设计水平和效率。 时序设计的另一个难点是它需要考虑到器件的逻辑单元。在FPGA器件中,器件的逻辑单元对时序设计的影响是非常大的,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。 时序设计是FPGA设计的关键组成部分,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。在FPGA设计中,时序设计需要考虑到各种因素的影响,包括器件的制造工艺、工作电压、温度等条件,时钟树的偏斜情况,建立时间和保持时间的要求,器件的竞争和冒险现象等。 在FPGA设计中,时序设计需要具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。因此,FPGA设计者需要不断学习和掌握新的时序设计知识和经验,才能不断提高设计水平和效率。 时序设计是FPGA设计的关键组成部分,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。在FPGA设计中,时序设计需要考虑到各种因素的影响,包括器件的制造工艺、工作电压、温度等条件,时钟树的偏斜情况,建立时间和保持时间的要求,器件的竞争和冒险现象等。 在FPGA设计中,时序设计需要具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。因此,FPGA设计者需要不断学习和掌握新的时序设计知识和经验,才能不断提高设计水平和效率。 时序设计是FPGA设计的关键组成部分,需要设计者具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。在FPGA设计中,时序设计需要考虑到各种因素的影响,包括器件的制造工艺、工作电压、温度等条件,时钟树的偏斜情况,建立时间和保持时间的要求,器件的竞争和冒险现象等。 在FPGA设计中,时序设计需要具备深入的知识和经验,才能正确地设计出高性能的FPGA系统。因此,FPGA设计者需要不断学习和掌握新的时序设计知识和经验,才能不断提高设计水平和效率。

剩余28页未读,继续阅读

- 粉丝: 1

- 资源: 22

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 十种常见电感线圈电感量计算公式详解

- 军用车辆:CAN总线的集成与优势

- CAN总线在汽车智能换档系统中的作用与实现

- CAN总线数据超载问题及解决策略

- 汽车车身系统CAN总线设计与应用

- SAP企业需求深度剖析:财务会计与供应链的关键流程与改进策略

- CAN总线在发动机电控系统中的通信设计实践

- Spring与iBATIS整合:快速开发与比较分析

- CAN总线驱动的整车管理系统硬件设计详解

- CAN总线通讯智能节点设计与实现

- DSP实现电动汽车CAN总线通讯技术

- CAN协议网关设计:自动位速率检测与互连

- Xcode免证书调试iPad程序开发指南

- 分布式数据库查询优化算法探讨

- Win7安装VC++6.0完全指南:解决兼容性与Office冲突

- MFC实现学生信息管理系统:登录与数据库操作

信息提交成功

信息提交成功