LVDS接口电路设计详解:低功耗高速传输的关键

133 浏览量

更新于2024-08-29

收藏 414KB PDF 举报

LVDS接口电路设计是现代高速电子系统中的关键组成部分,它利用低电压差分信号技术,实现了高数据传输速率、低功耗、噪声性能优异以及稳定性强的特点。LVDS技术的核心在于其小振幅差分信号传输机制,信号幅度仅约350mV,通过一对差分PCB线路或平衡电缆传递,显著降低了功耗和电磁辐射。与传统的ECL、BTL和GTL等高速器件相比,LVDS具有明显的功耗优势,特别适合对功耗敏感的高速数据总线应用。

1. 引言部分指出,高速电路设计中,尽管ECL、BTL和GTL等器件工艺成熟且广泛应用,但由于它们的功耗较大和容易产生电磁辐射,使得LVDS作为CMOS工艺的低电压差分信号解决方案显得尤为重要。LVDS器件的出现,为设计者提供了更为节能且性能稳定的接口选择。

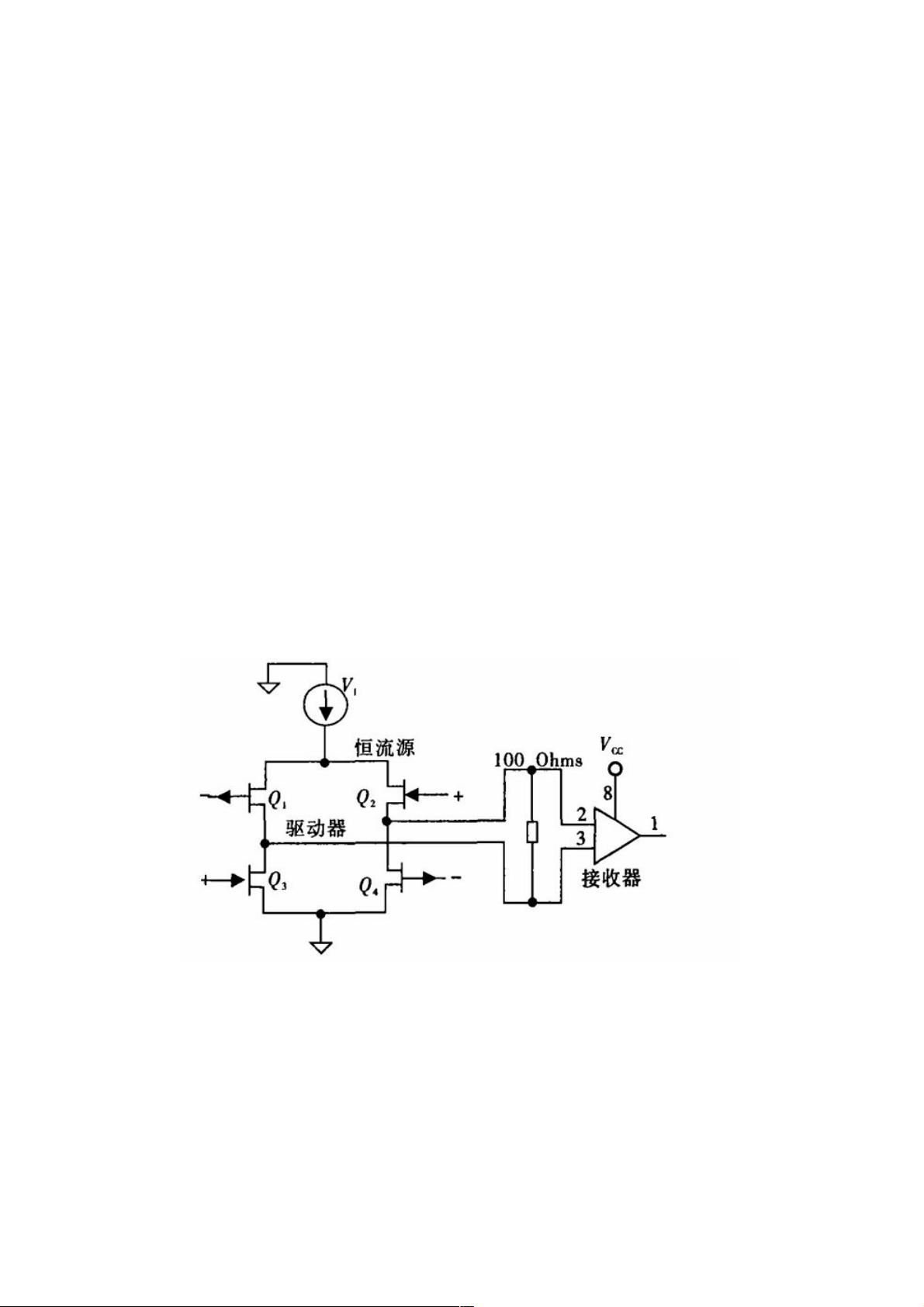

2. LVDS技术的详细介绍包括其工作原理。LVDS信号的恒流源模式驱动有助于减少噪声,使信号传输更加清晰。IEEEP1596.3和ANSI/EIA-644这两个国际标准规范了LVDS的电气特性,包括包交换编码和速率规格,确保了LVDS的通用性和适用性,支持多种应用场景和介质。

3. LVDS器件的工作涉及到接口设计的关键要素。设计时需注意信号的匹配、噪声抑制和信号完整性问题,特别是在与其他接口标准如LVPECL(低压电平正/负边缘逻辑)和CML(电流模式逻辑)之间的兼容性。不同耦合方式的选择,如直接耦合、变压器耦合或电容耦合,都会影响到信号的传输质量和可靠性,因此在设计时需要仔细评估并选择最适合的耦合方法。

4. 电路设计图展示了不同耦合方式下LVDS接口的具体实现,这些设计不仅涉及硬件连接,还包括了必要的信号调理和保护电路,以确保在实际应用中的稳定高效运行。

LVDS接口电路设计是一个综合性的技术领域,涉及信号传输原理、电气特性标准、接口兼容性分析以及具体实施中的设计策略。通过优化这些设计,可以在高速数据通信中实现高效的能源利用和信号质量的提升,对于现代电子系统的性能提升和能耗控制具有重要意义。

498 浏览量

297 浏览量

点击了解资源详情

257 浏览量

498 浏览量

924 浏览量

721 浏览量

327 浏览量

3129 浏览量

weixin_38637272

- 粉丝: 4

- 资源: 935

最新资源

- RCP程序设计.pdf

- MQC mercury quality center 官方中文帮助文档

- NetJava.cn--《velocity Java开发指南中文版》.pdf

- Java项目开发常见问题

- velocity用户手册.doc

- 经典<加固linux-HardeningLinux>英文版

- 网络原理课件(4)-数据链路层

- Spring Guide SpringGuide.pdf

- iBATIS-SqlMaps-2_cn.pdf

- 计算机病毒原理.ppt

- 揭秘jbpm流程引擎内核,希望能使大家得到帮助

- 数控机床旋转进给系统的状态空间模型及性能分析

- 关于STC单片机编译软件KEILC51

- POJOs.in.Action

- Groovy的最新教程,来看看吧

- ibatis 开发指南 ibatis 开发指南.pdf